Incremental analysis

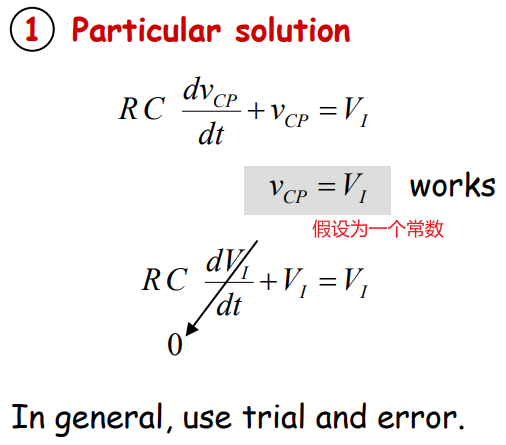

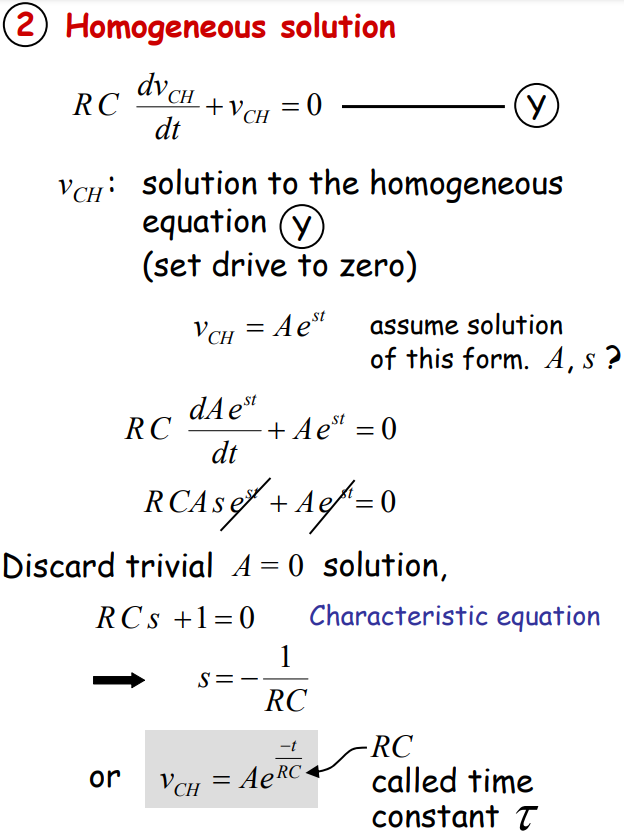

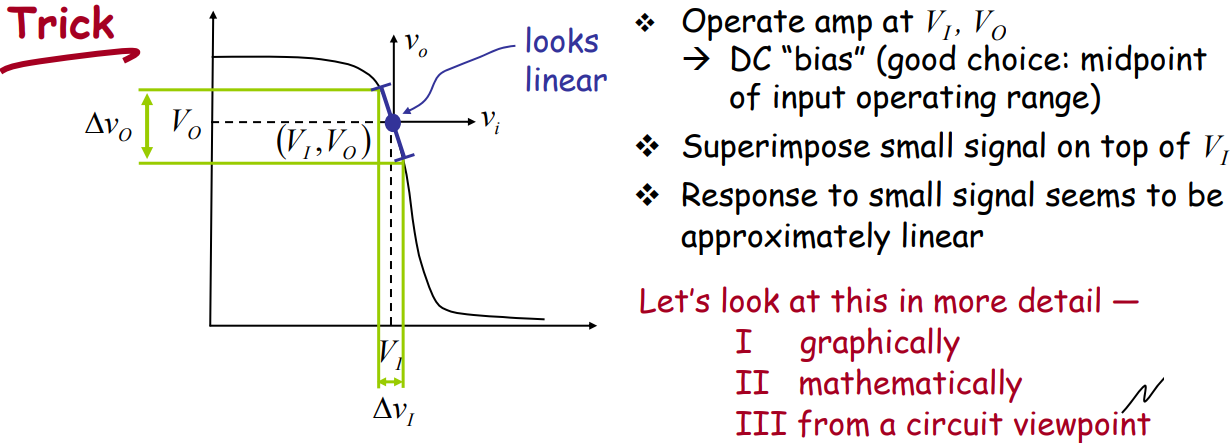

如何解决上面信号的distortion的问题,即一个正弦信号,经过一个nonlinear device(其实也是一个transfer function)作用后,输出的是一个非正弦信号。答案就是【zen】(禅宗):你必须在一个院子里坐下,注视地上的一块小石头,你专注于它,直到地球上的其他一切都消失。好了,回到现实,就是你只关注transfer function上非常小的一段,这样在这非常小的一段内,可以近似认为是线性的,但是注意此时的线性是存在offset的。那么我们只需要做如下两个事情:

- boost,抬升电压的大小为\(V_D\),抬升后,LED两端的电压围绕\(V_D\)为中心,上下对称波动;

- shrink,即减少正弦波的振幅,也就是将正弦波的波峰和波谷压缩到正好对应于所选取的LED 特性曲线中那一小段线性区所对应的的最大电压和最小电压;

上述处理方法,人们常称之为incremental analysis/small signal method/small signal analysis。

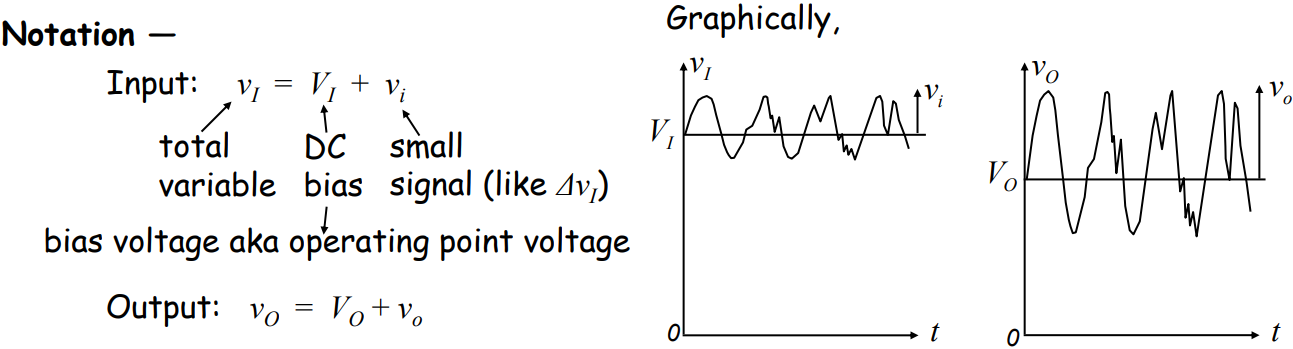

输入:offset的部分用\(V_D\),小信号用\(v_d\)表示,总信号用\(v_D\)表示;

输出:offset的部分用\(I_D\),小信号用\(i_d\)表示,总信号用\(i_D\)表示;

这种曲线变直线的方法,mathematically来说,就是泰勒展开的一阶近似,此处即LED等效为一个固定的电阻。数学语言的描述这里我们不赘述,参考本节PPT。

Dependent Sources and Amplifiers

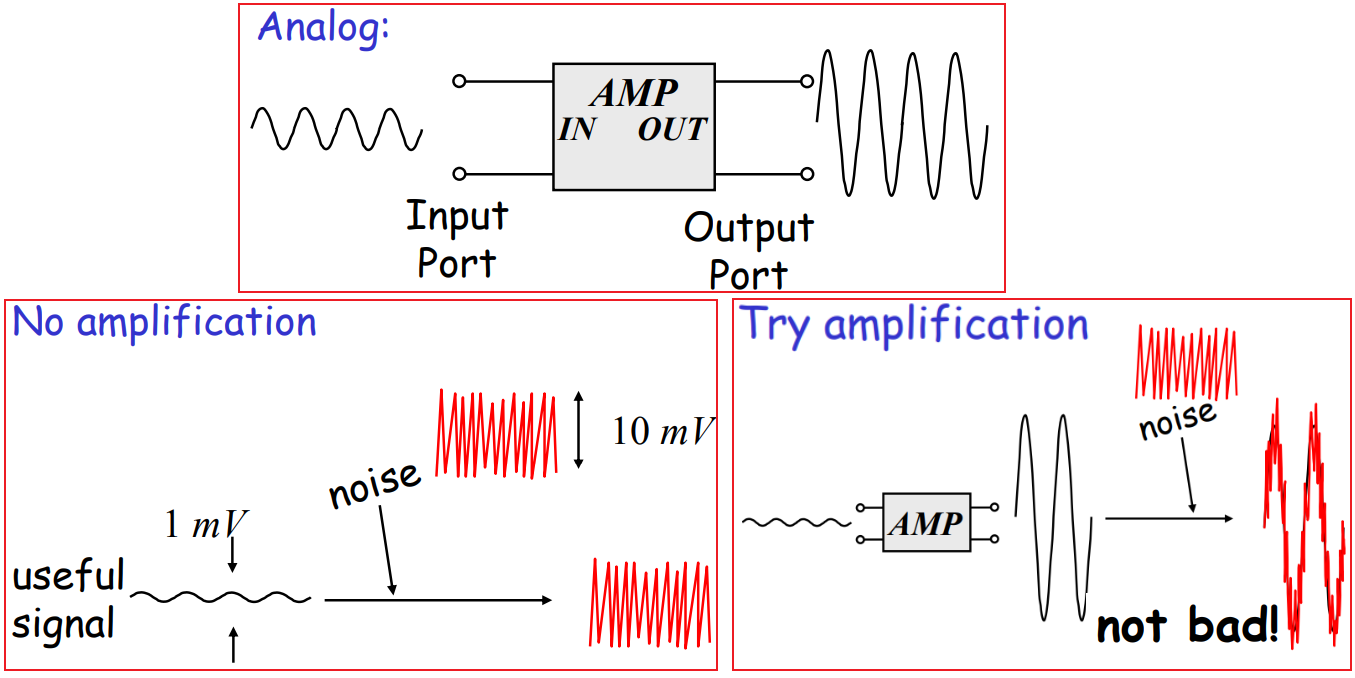

Amplifiers

- Signal amplification——key to both

- analog and digital signal processing

- noise tolerance during communcation

- 模拟信号向数字信号转换需要信号的强度是一个特定值,这样才能转换成数字电平,所以如果原始模拟信号很小,就要利用放大器放大。

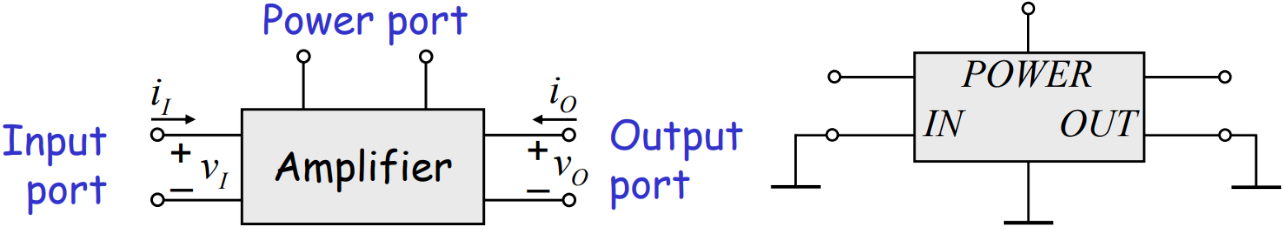

- 通常放大器除了有输入和输出,还可能包含电源端口(power port),因为放大的信号意味着信号功率的增益。

模拟信号的放大:

数字信号的放大:

再谈放大器:

- We often don't show the power port.

- Also, for convenience we commonly observe "the common ground discipline". In other words, all ports often share a common reference point called "ground".

Dependent Source

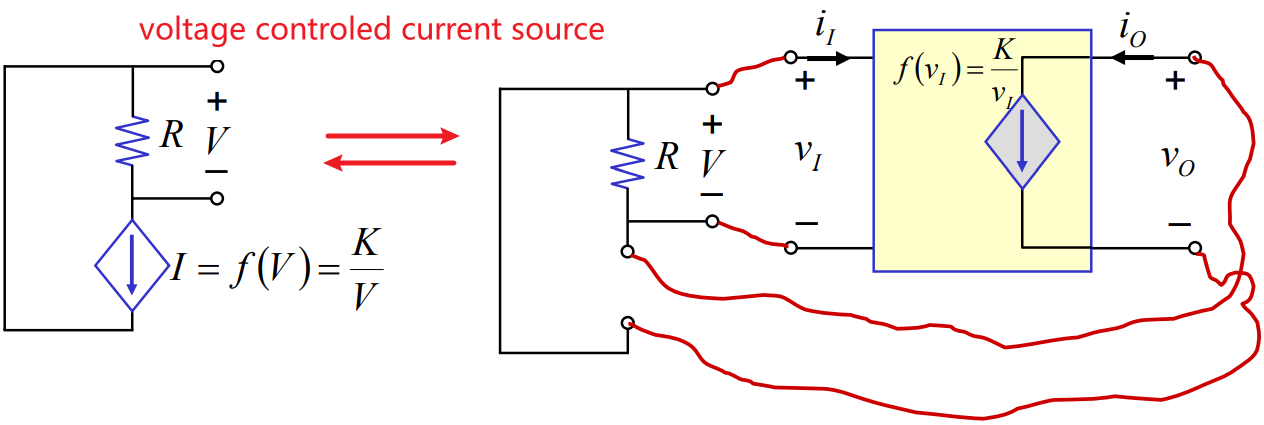

【dependent source】是一种新的device,如果看作黑箱的话,那么有control port和output port,每个port分别有正负两个接线端,如图所示。

可以有多种形式:

可以有多种形式:

- Voltage Controlled Current Source :简写为【VCCS】,也就是Current at output port is a function of voltage at the input port,比如MOSFET;

- Current Controlled Voltage Source 【CCVS】

- Voltage Controlled Voltage Source 【VCVS】

- Current Controlled Current Source 【CCCS】

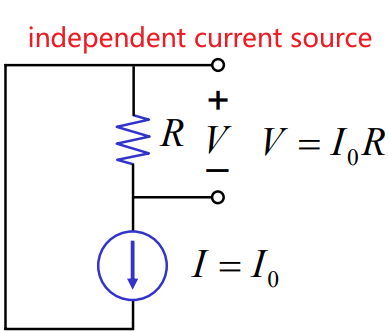

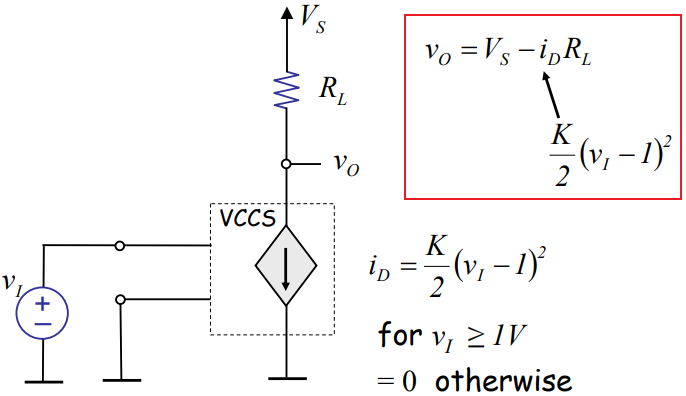

下面分别展示我们之前就接触过的independent current source,然后对比新学的device (dependent),即VCCS。

通常情况下,当控制端口对电路没有任何其他影响的时候(比如汲取被控电路的电流或者分压),就可以去除,不用明确地显示出控制端口,只画出输出端口即可。你可以简单地认为输出电流/电压受控于无论什么你想到的变量。你可以画出这样的菱形,让后在旁边写下关系式即可。你要记住,受控源只不过是一种的小的电路元件。

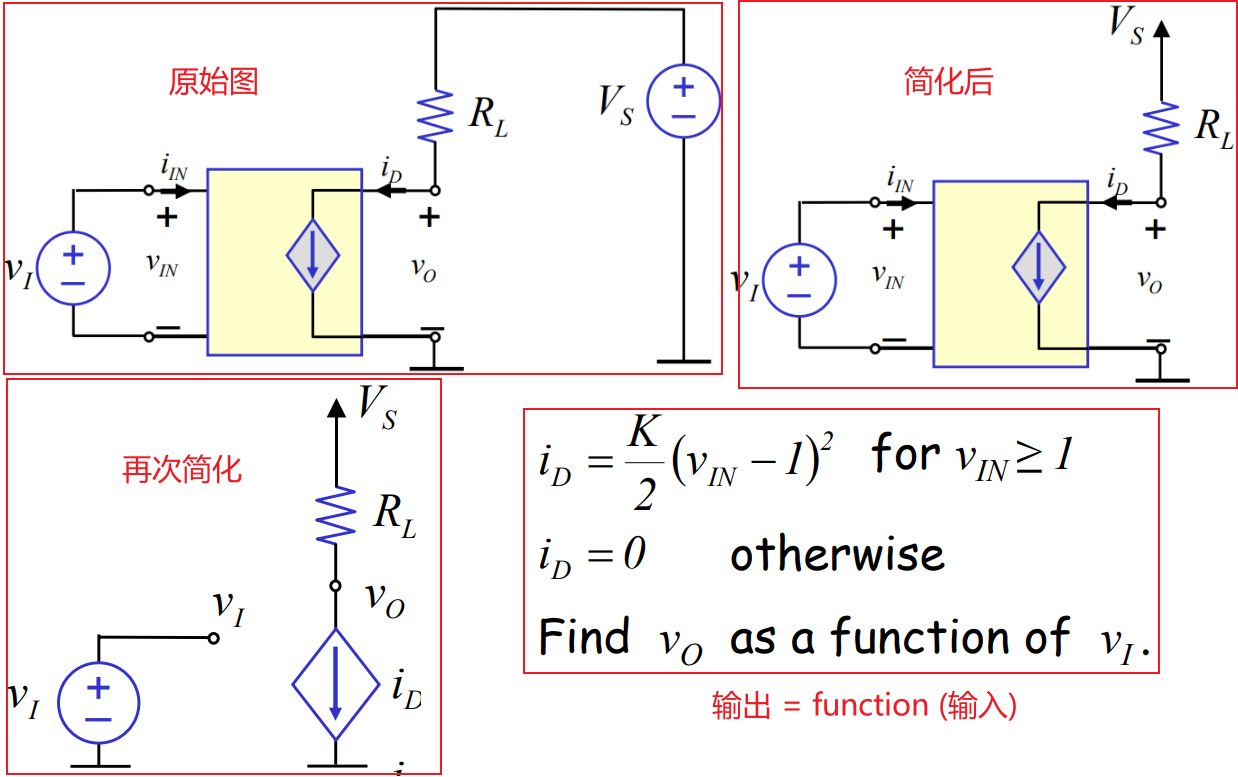

下面再展示另一个Voltage Controlled Current Source,而且表现出放大功能。

求解过程

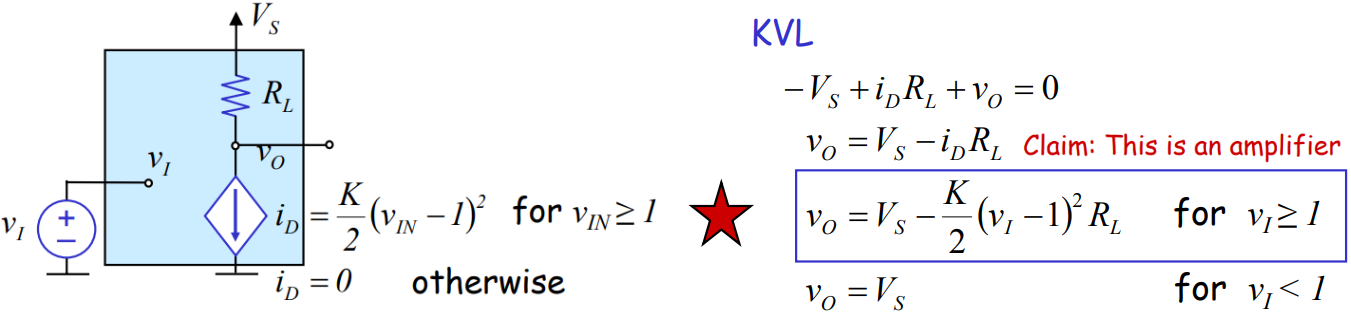

where's the amplification? 我们给定一些参数之后,就可以得到上面蓝色框中更具体的表达式了。

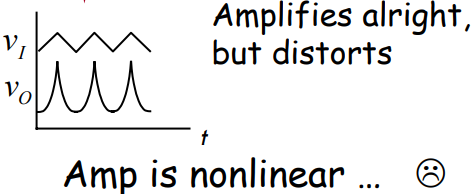

注意我们这里得到的所谓的放大器是一个劣质的放大器(crummy amplifier),因为放大系数是变化的。

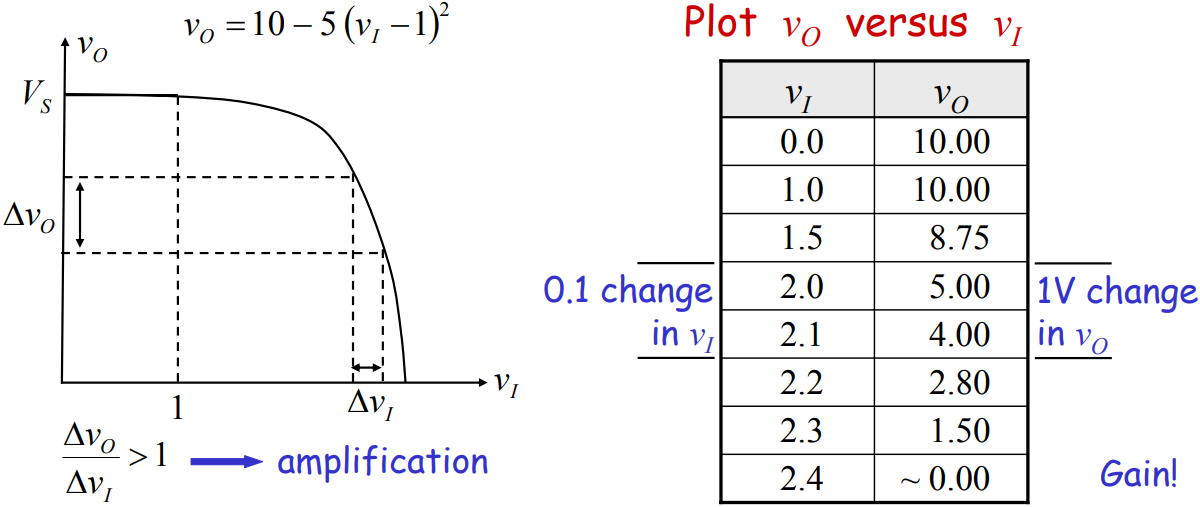

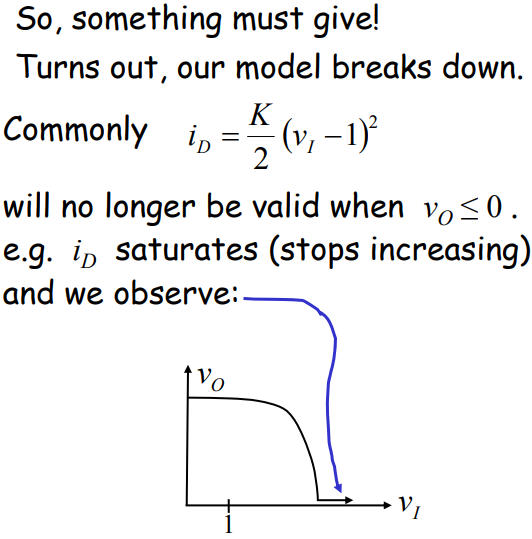

根据上面的公式\(v_O=10-5\left(v_I-1\right)^2\),我们知道从数学的角度看,随着\(v_I\)的不断增大,于是\(v_O\)会加速下降,从正值慢慢变为零,然后降到零以下,但是这只是mathematically predicted behavior,实际情况又是什么样的呢?

- If VCCS is a device that can source power(就是说VCCS向外供电), then the mathematically predicted behavior will be observed(也就是上图的曲线可以降到零,然后继续降为负值).

- 如果VCCS是一个无源设备(passive device),那么它就不能source power,于是物理上\(v_O\)不可能为负值。那么不断增大\(v_I\),使得\(v_O\)靠近零,此时会发生什么呢?难道是按照上面的数学公式,可以无限逼近上图的交点,只是不能取到吗?

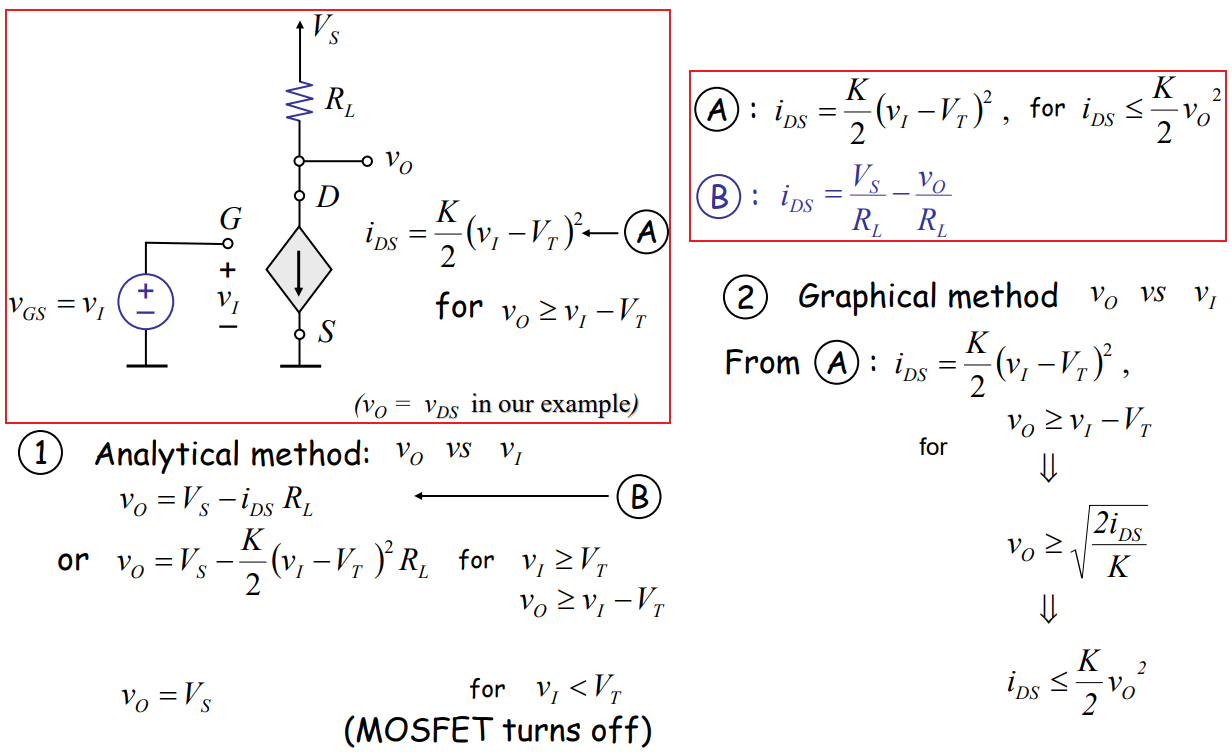

MOSFET amplifier-large signal analysis

大信号分析(large signal analysis)其实就是观察一个电路,比如含有MOSFET,然后想办法让设备以一种方式运作,从而让MOSFET总是处于饱和,你必须figure out参数的设定。尽管这里我们是以MOSFET为例,但是同样的分析方法也适用于其他device,比如BJT(Bipolar junction transistor)。

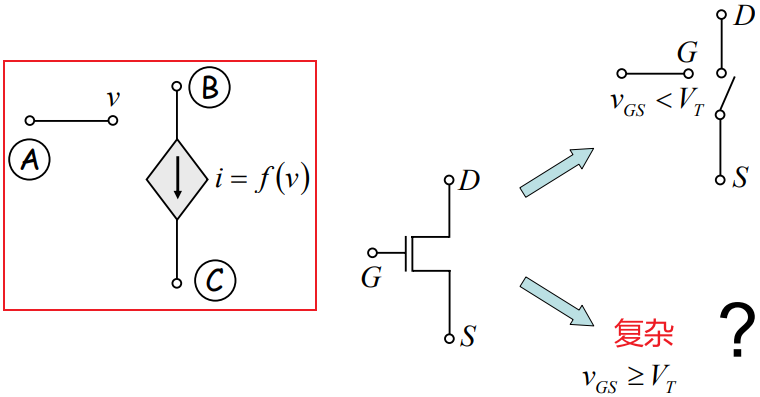

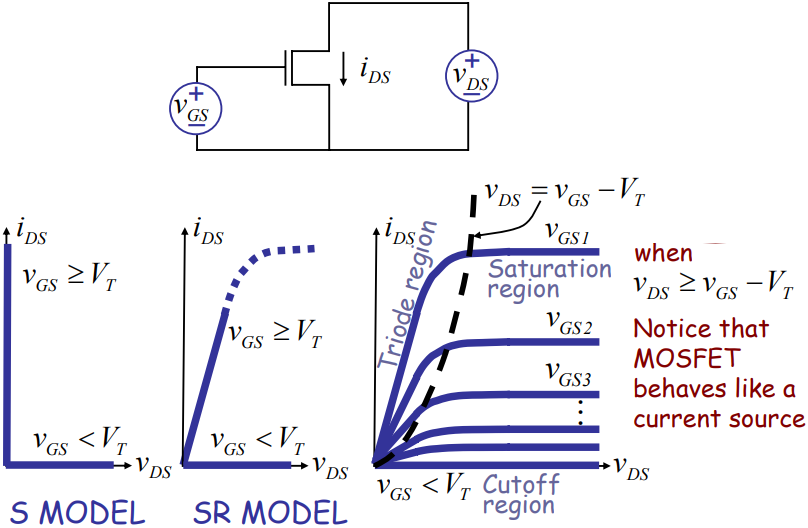

我们的老朋友MOSFET是一个VCCS器件,即drain和source之间的电流是gate电压的函数\(i=f(v)\)。对于MOSFET的分析,我们从理想的S Model到SR Model,但是实际上对于MOSFET的on-state(通路状态)来说,it turns out that in real life the behavior of the MOSFET between the drain and the source terminals, is much more complicated than the limited form in which you saw it. 今天要做的就是脱掉MOSFET的神秘包装。

下面Graphically对比S model,SR model以及实际的MOSFET的characteristic。

【Switch Current Source Model】(SCS model)

When \(v_{G S} \geq V_T\), and also \(v_{D S} \geq v_{G S}-V_T\), the MOSFET is in its Saturation Region, and the SCS model of the MOSFET is more accurate than the S or SR model. 此时MOSFET放弃抵抗躺平了(即\(i_{D S}\)不再随着\(v_{D S}\)的增长而增值,而是保持不变),MOSEFT就会在drain and source之间表现出电流源的特性,所以我们用SCS model MOSFET as a current source in that part。注意SCS model的范围仅限于\(v_{D S}>v_{G S}-V_T\)的阶段(即上面黑色虚线的右侧)。

- S model— just for fun!

- SR model—在整个数字电路design中,我们关注SR model。比如一个下拉的MOSFET管开启的时候,或者许多MOSFET管开启的时候,输出电压就被拉到接近GND,所以\(v_{D S}\)很小,应用SR model make sense. ;

- SCS model—在模拟电路,比如放大器设计,we will operate the MOSFET in a a saturation regeion,必须遵守饱和规则,就是说将工作在饱和区的MOSFET管作为一个电流源。

Note: alternatively (in more advanced courses)

\(v_{D S} \geq v_{G S}-V_T\) use SCS model

\(v_{D S}<v_{G S}-V_T\) use SR model

or, use SU Model (Section 7.8 of A&L) 参考这里:Switch Unified (SU) MOSFET Model

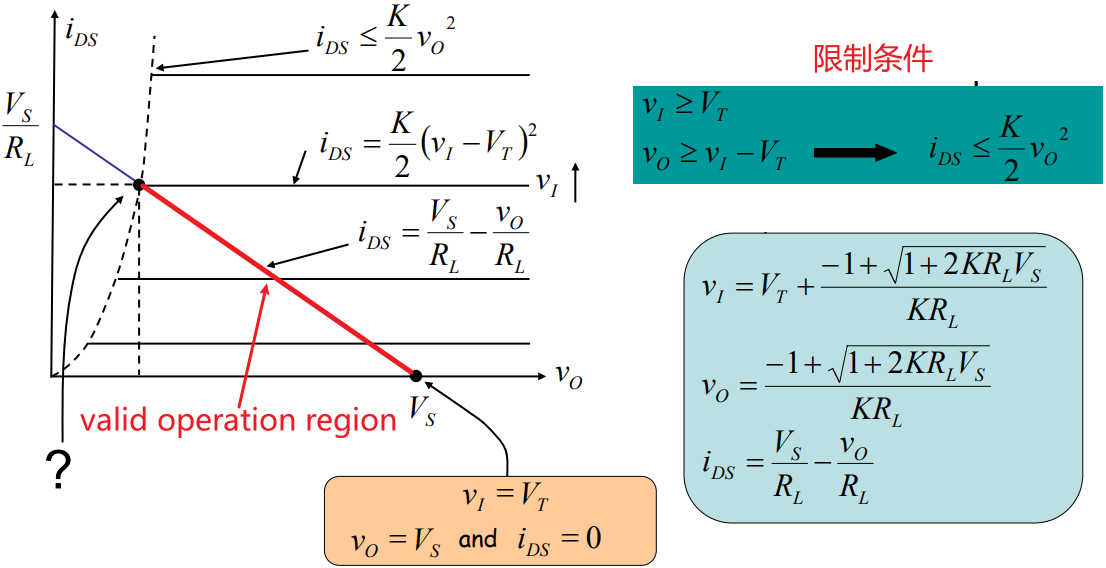

Let's analyze the circuit. First, replace the MOSFET with its SCS model. 那么在给定电路元件和连接方式,以及control port (GS端)的电压的情况下,\(v_O\)以及\(i_{D S}\)是多少呢?下面用图像法形象展示求解方法。(啰嗦一句\(v_O \geq v_I-V_T\)即处在饱和区)

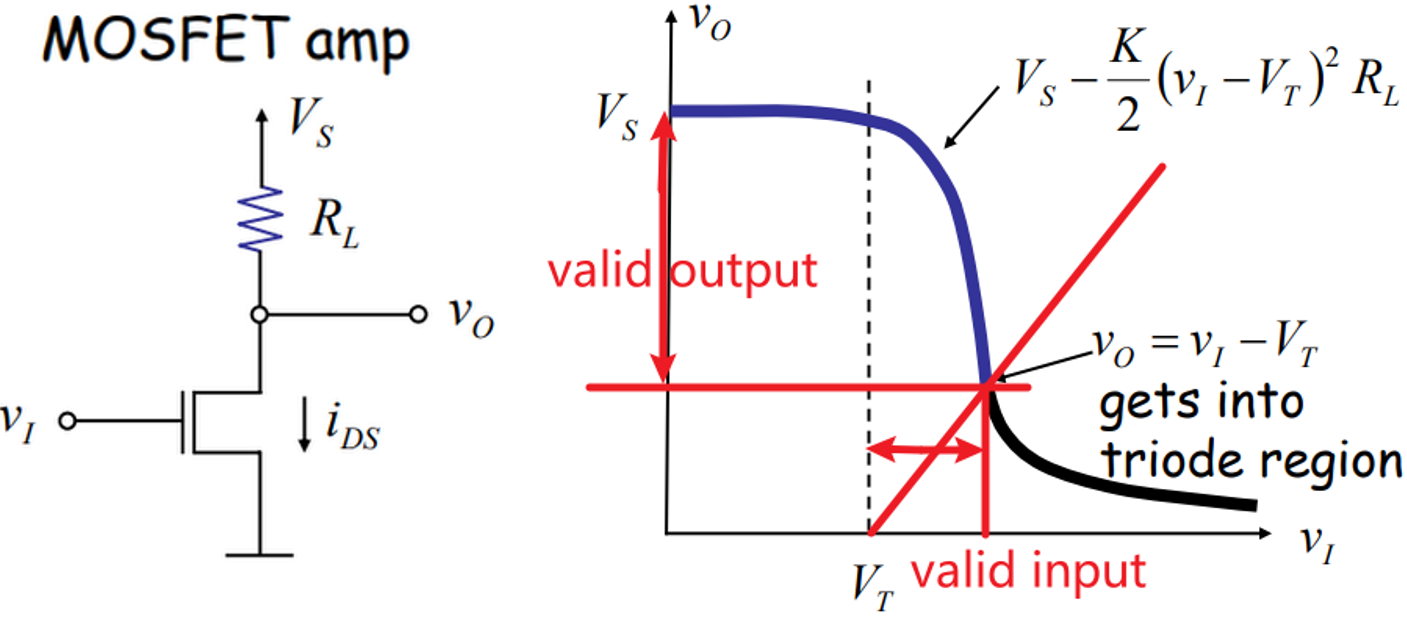

在实际应用中,无论是MOSFET还是其他的BJT等等,我们都很关心其对应功能的工作区间,既有输入的工作区间,也有输出的工作区间。对于MOSFET要实现放大功能,那必须在saturation discipline下,下面分别从\(v_O\) versus \(v_I\)传递函数,以及负载线的角度求解 input/output operating range。

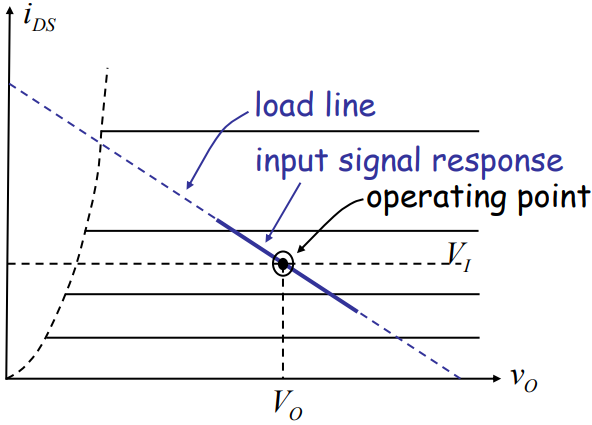

下图中的红色负载线和饱和区(多条水平实线)是两个constraints,必须同时满足,即需要求解给定\(v_I\)下两条线的交点,该交点对应的电流

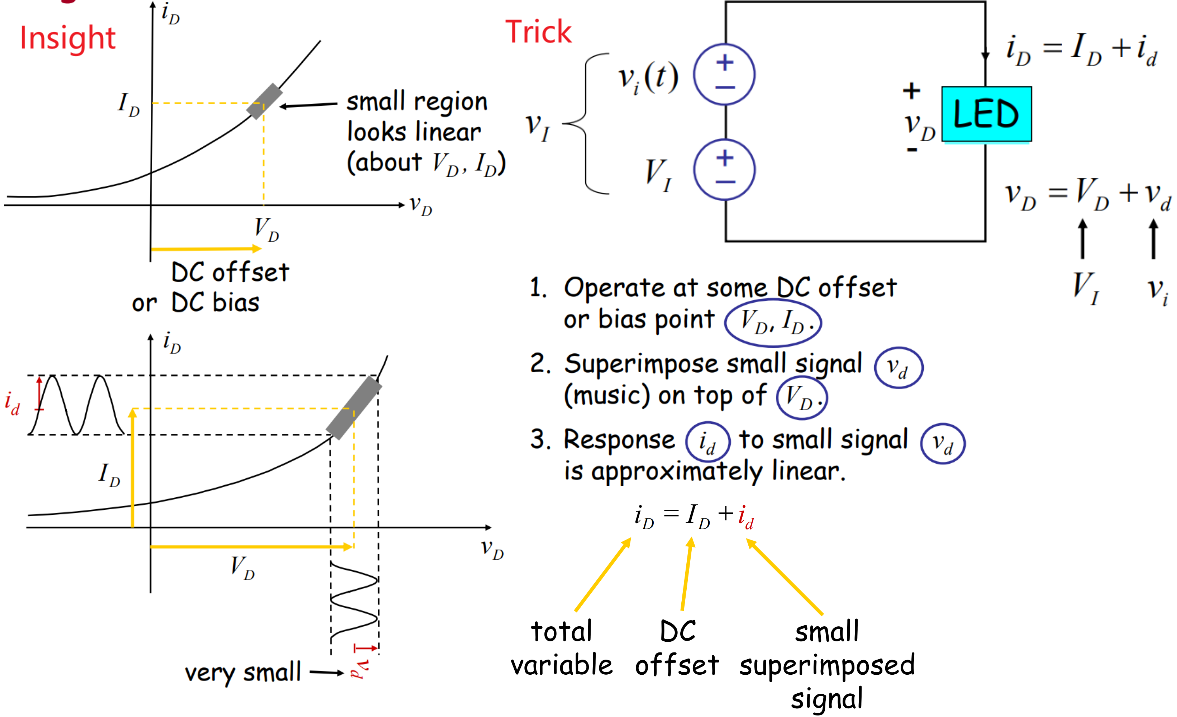

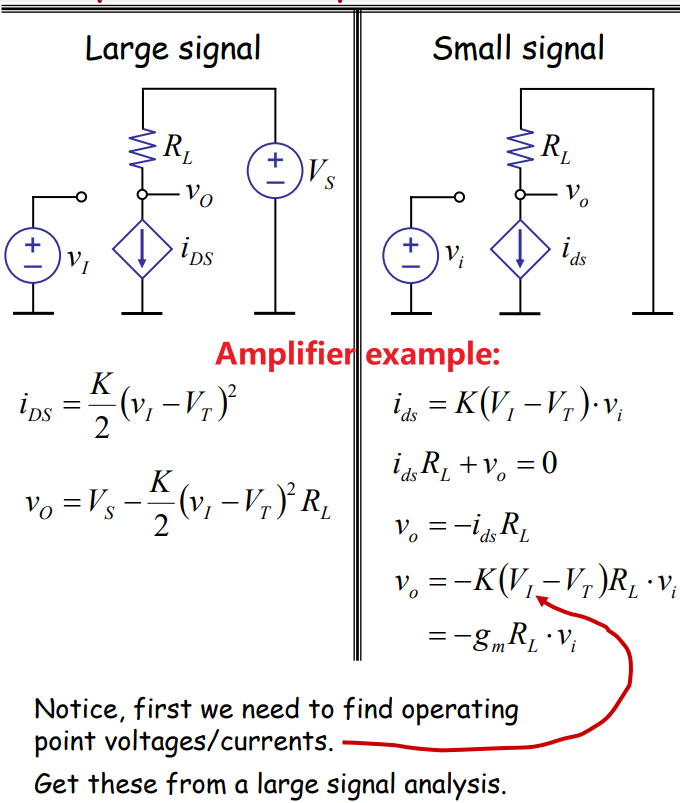

Amplifiers - small signal model

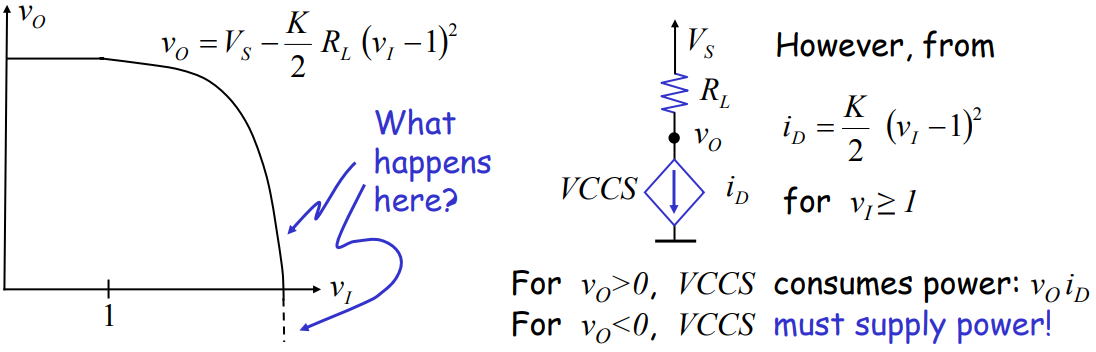

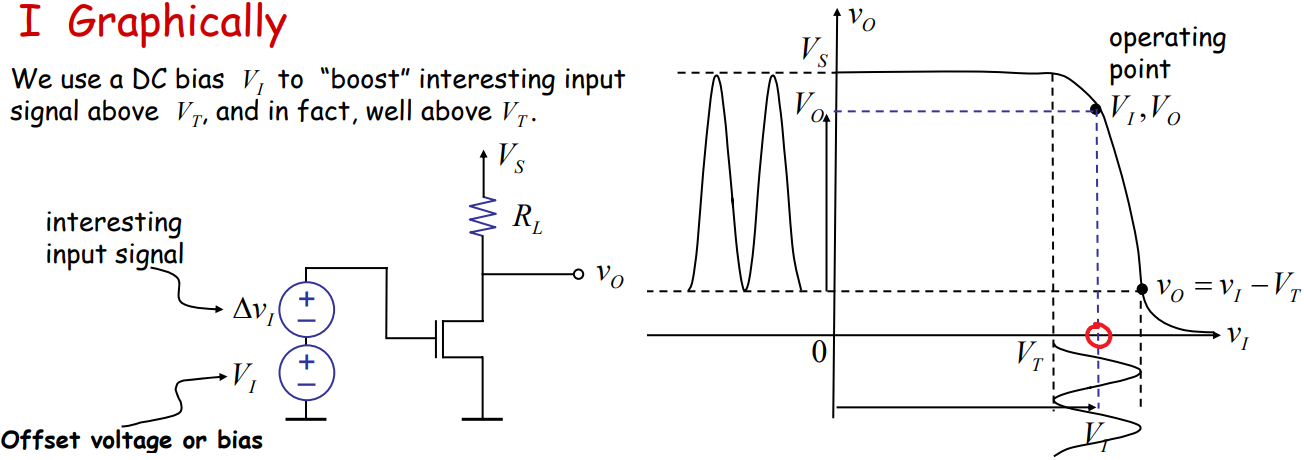

对于上面讨论的MOSFET,我们会碰到之前在学习放大器的时候遇到过的问题,即放大过程会导致放大后信号的distortion,即不能实现线性放大。这里我们采用的方法同样是禅宗,即只专注输入-输出电压关系式曲线上的一小段。

对于上面讨论的MOSFET,我们会碰到之前在学习放大器的时候遇到过的问题,即放大过程会导致放大后信号的distortion,即不能实现线性放大。这里我们采用的方法同样是禅宗,即只专注输入-输出电压关系式曲线上的一小段。

Good choice for operating point: midpoint of input operating range. 即上图红色圈出的。

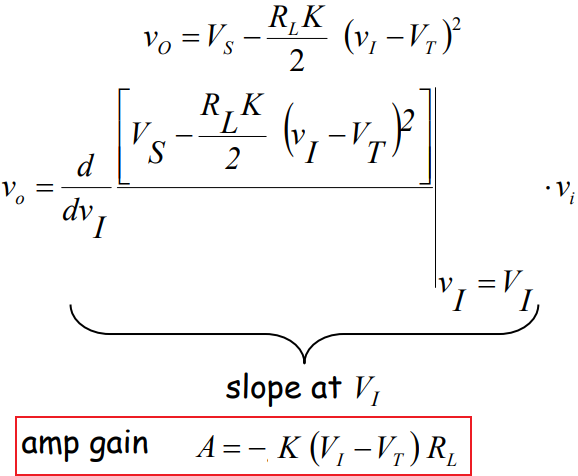

第二种Mathematically的处理方法,除了基于\(v_O=V_S-\displaystyle\frac{R_L K}{2}\left(v_I-V_T\right)^2\)将自变量和应变量改写为offset + small signal,还可以直接用

How to choose the bias point:

- gain:\(A=-K\left(V_I-V_T\right) R_L\)

- gain component:\(g_m=K\left(V_I-V_T\right)\)被称作【跨导】(transconductance),叫这个名字是因为它在某种程度上反映了对输入的传导能力。

- \(g_m\) is constant for fixed DC bias

- 如果偏置点选择不当,当信号变大时可能被截断或者产生失真distortion

- Input valid operating range. Bias at midpoint of input operating range for maximum swing. 比如你想在正半周和负半周获得同样的偏移。

老师上课提了一个问题:上面我们讨论的是将一个小信号放大,那么如果你想将一个本来就很大的信号放大到更大,该怎么办呢?实际上通过器件的电流越大,产生的各种噪声也越大,因此一个强大的放大器也许并不适合处理非常弱的信号,因为它们有较大的固有噪声,因此对于噪音敏感。

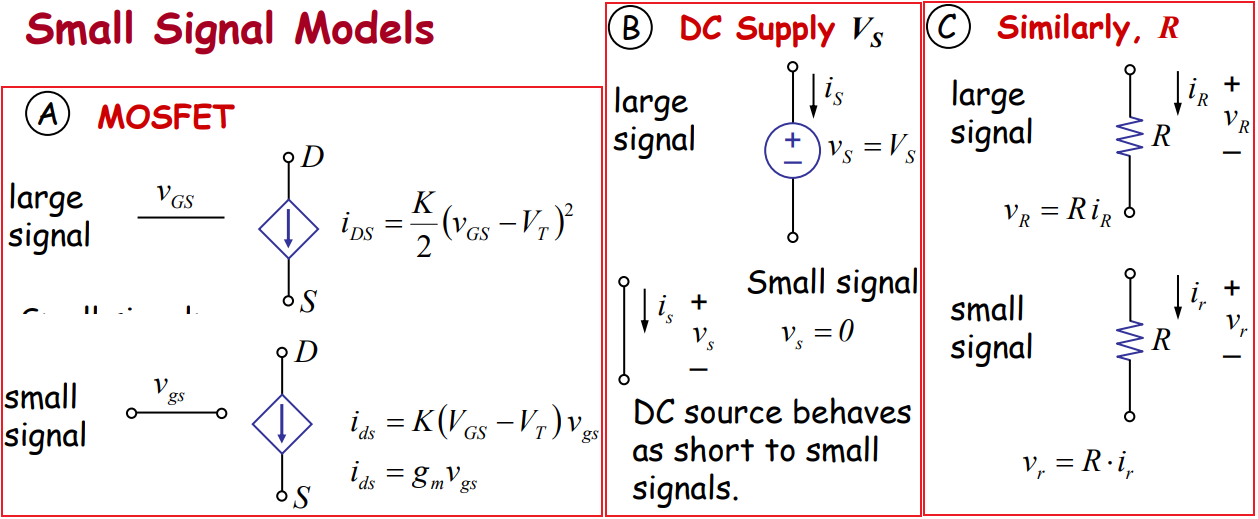

The Small Signal Circuit View

- We can derive small circuit equivalent models for our devices, and thereby conduct small signal analysis directly on circuits.

- We can replace large signal models with small signal circuit models.

- KVL和KCL只是电路的不同表达方式而已,因为它们其实都表达了这个电路的拓扑结构。记住任何一个KVL等式都代表了一个回路,任意一个KCL表示节点的连接方式。

- To find the relationship between the small signal parameters of a circuit, we can replace large signal device models with corresponding small signal device models, and then analyze the resulting small signal circuit. 也就是说之前的KCL和KVL等式中的large signal可以用small signal + bias来替代,而作为不变量的所有bias对等式的影响就是一个常数,因此我们可以用所有small signal变量构建出新的KCL/KVL等式。

Small Signal Circuit Analysis

- Find operating point using DC bias inputs using large signal model.

- Develop small signal (linearized) models for elements.

- Replace original elements with small signal models.

- Analyze resulting linearized circuit…

Key: Can use superposition and other linear circuit tools with linearized circuit!

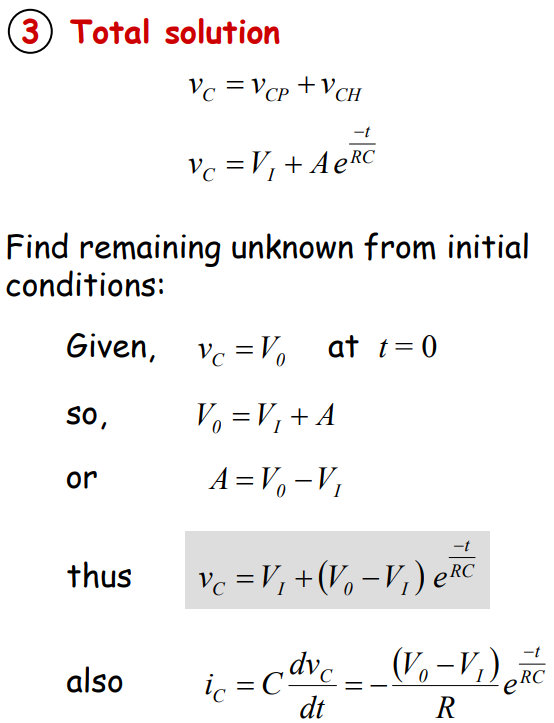

Capacitors and first-order systems

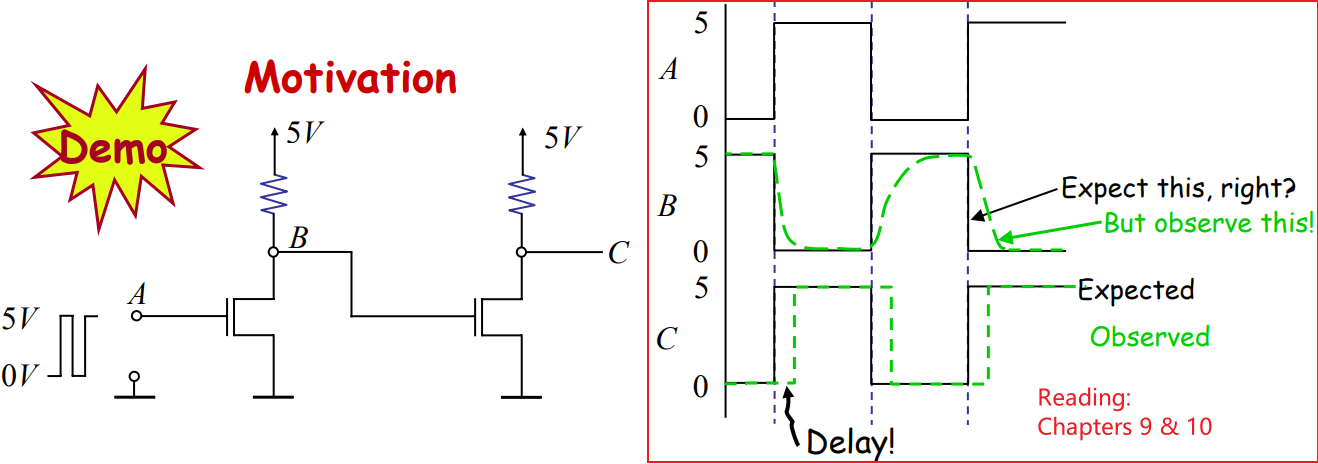

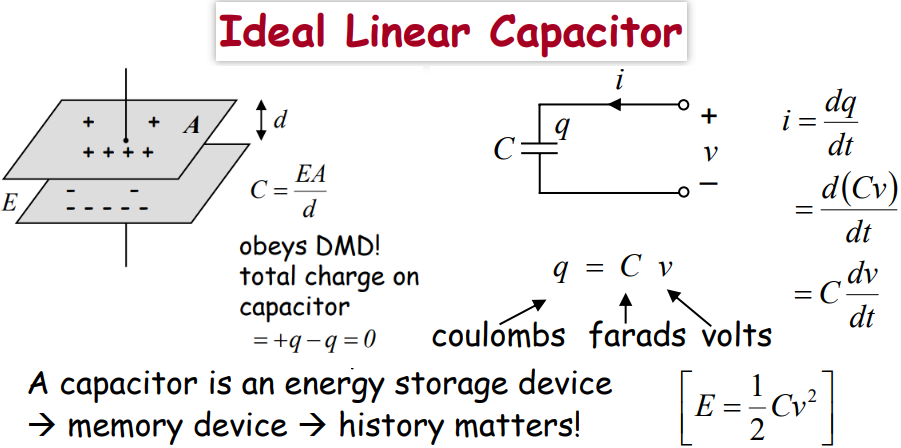

之前讨论的device,比如inverter或者NAND gate都不具有记忆性,即某时刻的输出只和该时刻的输入相关,与其输入的历史无关。下面介绍的电容具有记忆性,即输出不仅仅由当时的输入决定,而且和电路过去所处的状态有关。Past is going to matter!

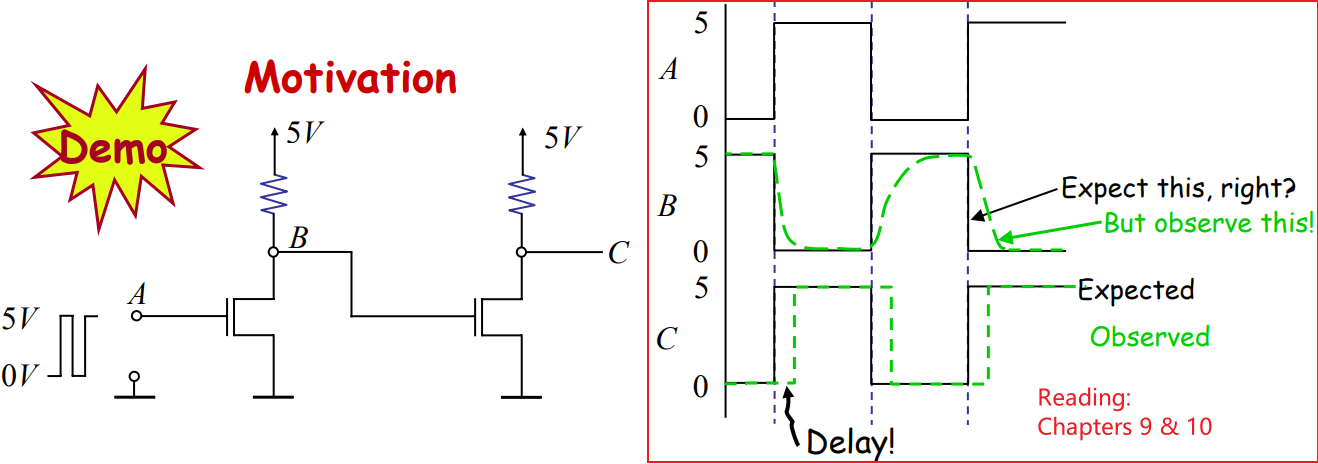

Anant Agarwal:这个无法回避的事实,这一点点延迟正是一直以来我们每隔几年就需要更换电脑的原因。如果没有这个延迟,我们只需要买一台电脑,然后用一辈子,Intel可能一年之内赚一大笔钱,然后就没了。但就是因为这个小小的区别,整个半导体都在不停地发展,试图改变这个延迟,或者说图中的反向器延迟inverter delay。产生这种现象的原因是电路中引入了一种特殊的元件,至今我们还没介绍。半导体产业的一大部分及后续课程和设计等等,都致力于如何使延迟更小,怎么让响应更快,这关系到我们能把奔腾4处理器提高到多高的频率。你下面将学到非常酷的东西,它对我们的生活有巨大的意义。

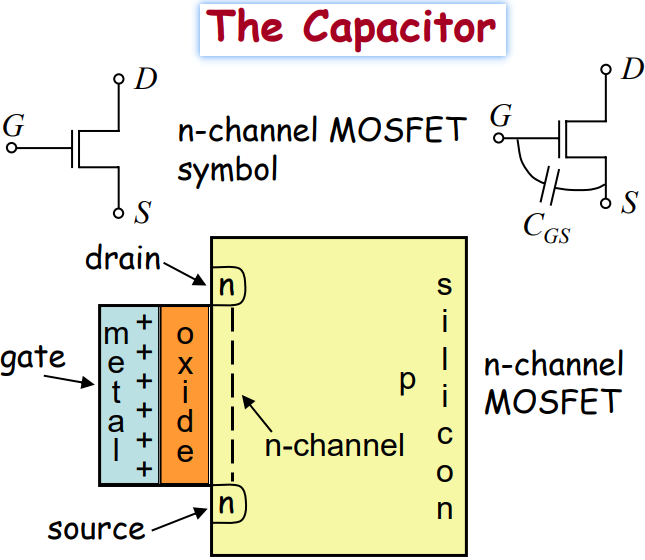

延迟来自于,在第二个反相器的栅(gate)和源(source)之间的电容。在我们之前处理的元件中,\( dq/dt\)任何时候都应该为零,即满足集总LMD。那么对电容来说如何处理呢?其实电容也是遵守LMD,只要我们把电容的上下两块板看作一个整体作为研究对象,那么它的净电荷还是零,因此电容还是在我们之前集总的大操场上。

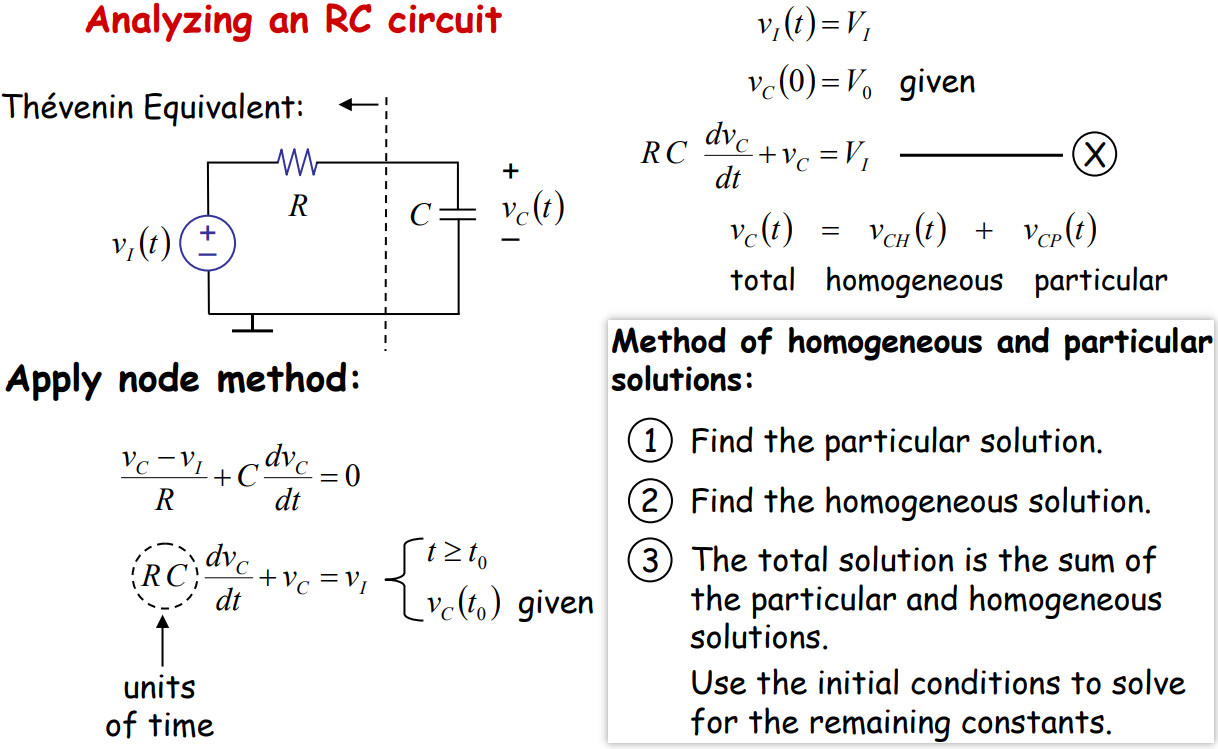

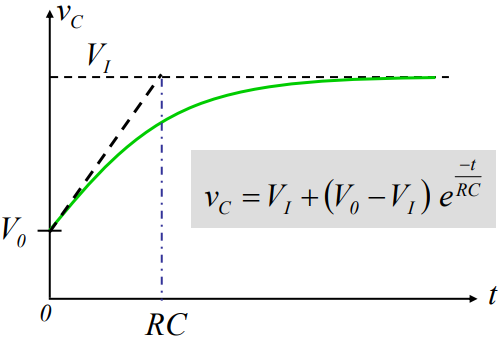

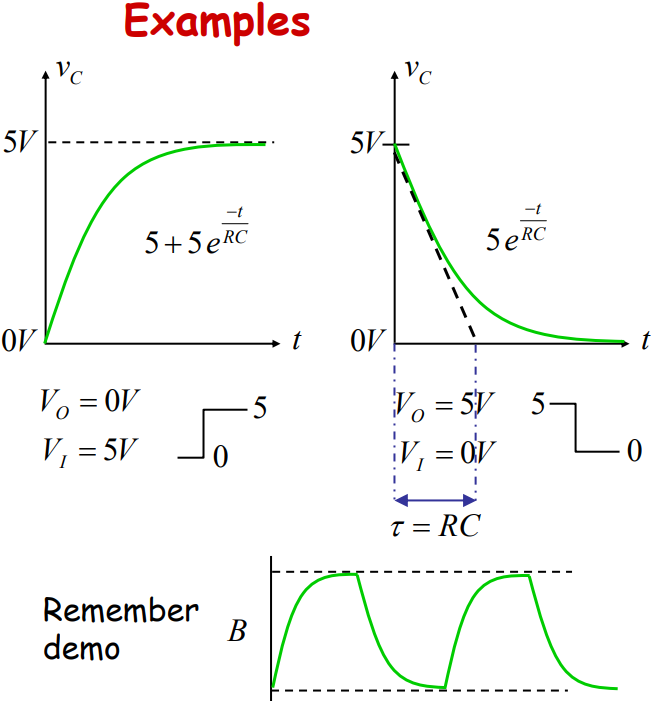

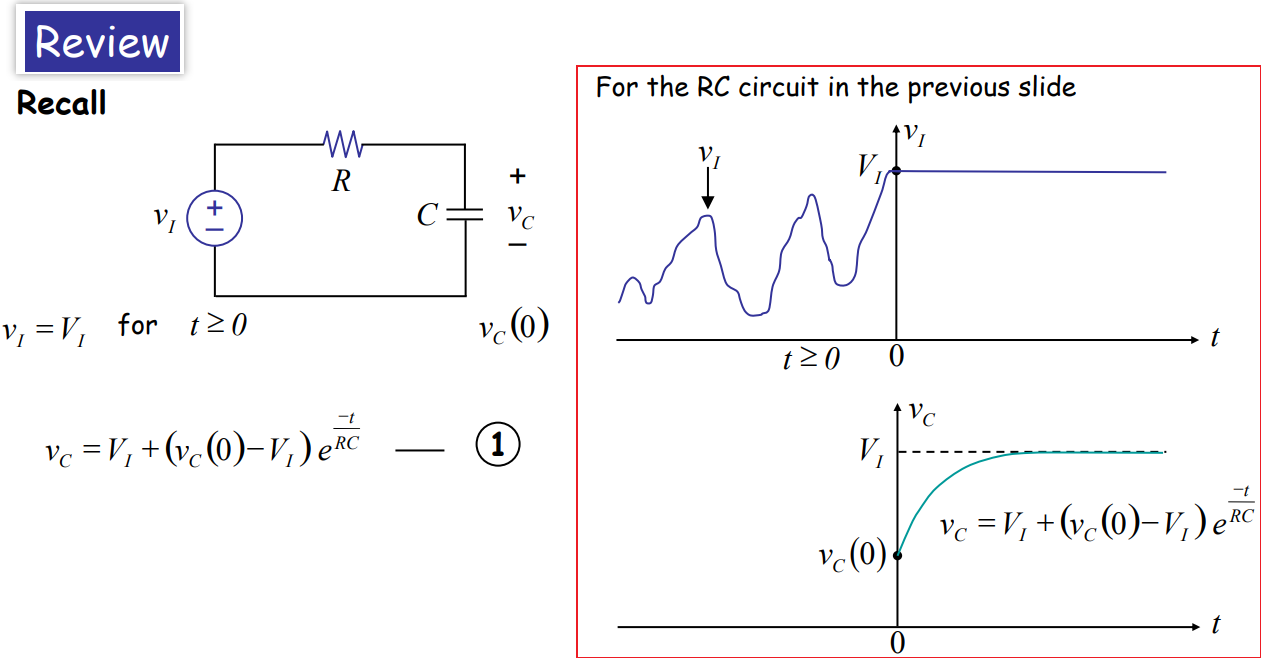

注:无论是增长的指数还是衰减的单指数函数,在\(t=0\)函数点处做切线,交时间轴于RC,即电路的【时间常数】(寿命)。

【特征方程】(Characteristic equation), 在RC电路还有其他形式中一再见到它。特征方程在MIT-微分方程中也有讨论。这里完全是用数学得到了最终解,就像我一直以来承诺的一样,下节课我会给你们一个直觉的EE方法,因为真正的EECS folks不会用上面的数学方法去处理这类问题,真正的EECS folks用直觉,下节课我会教你们如何用简单的4步得到答案。

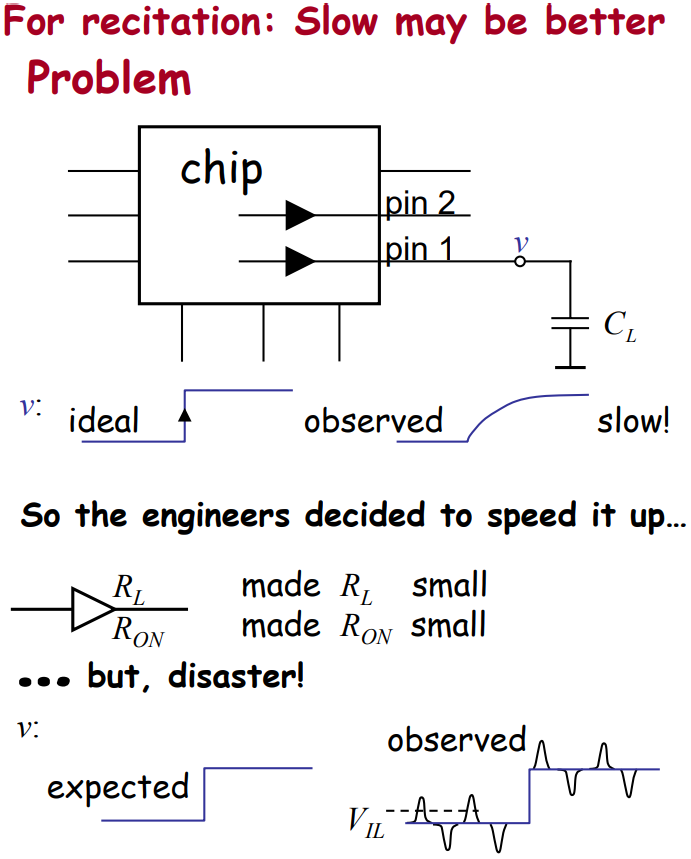

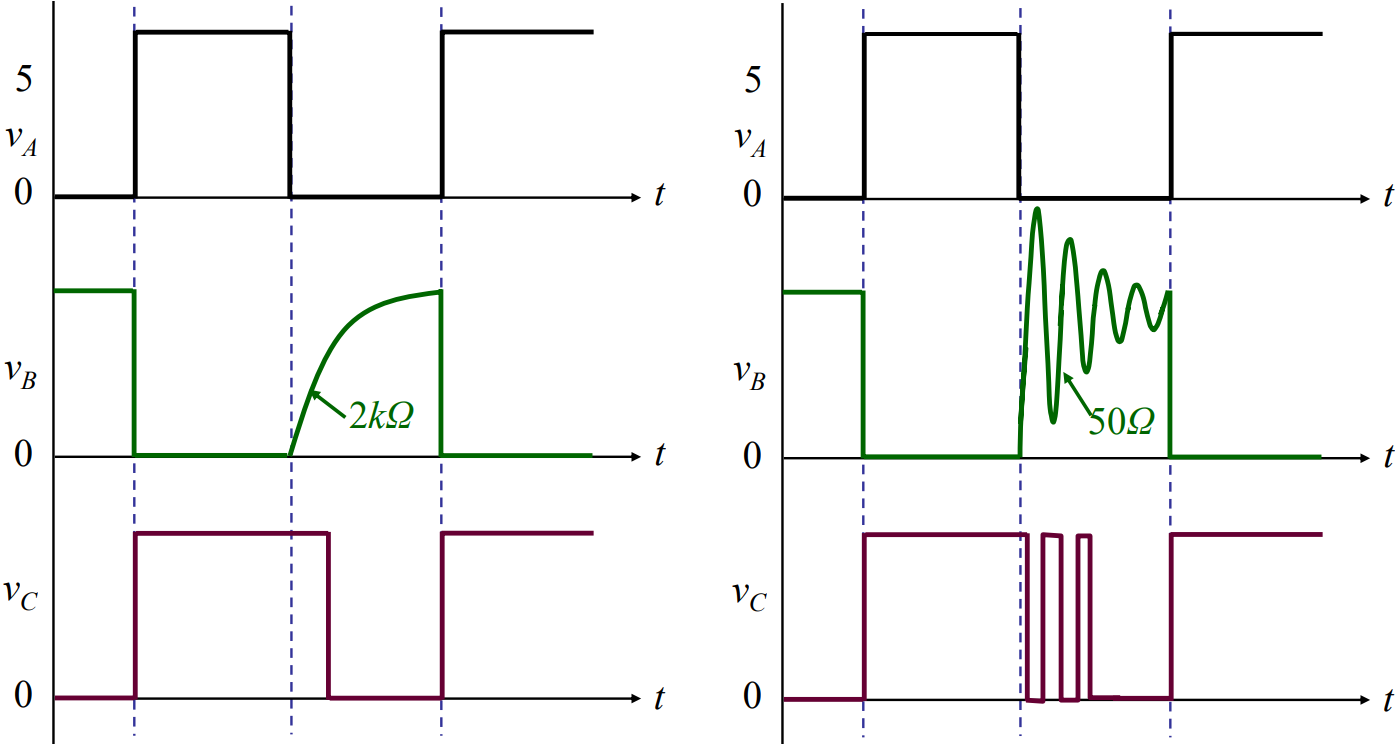

Digital circuit speed

这一节,我们的例子是一个反相器(X)去驱动另一个反相器,然后观察延迟的情况。根据上一节的知识,我们将计算上升过渡的延迟值\(t_r\),和下降过渡的延迟值\(t_f\)。输入端A点是快速变化的(高低电平切换),但是intermediate node B rise much slowly,因此最终的输出(node C)的变化要延后于A,即下图中绿色线(实际观测到的B、C两点的电压变化)。

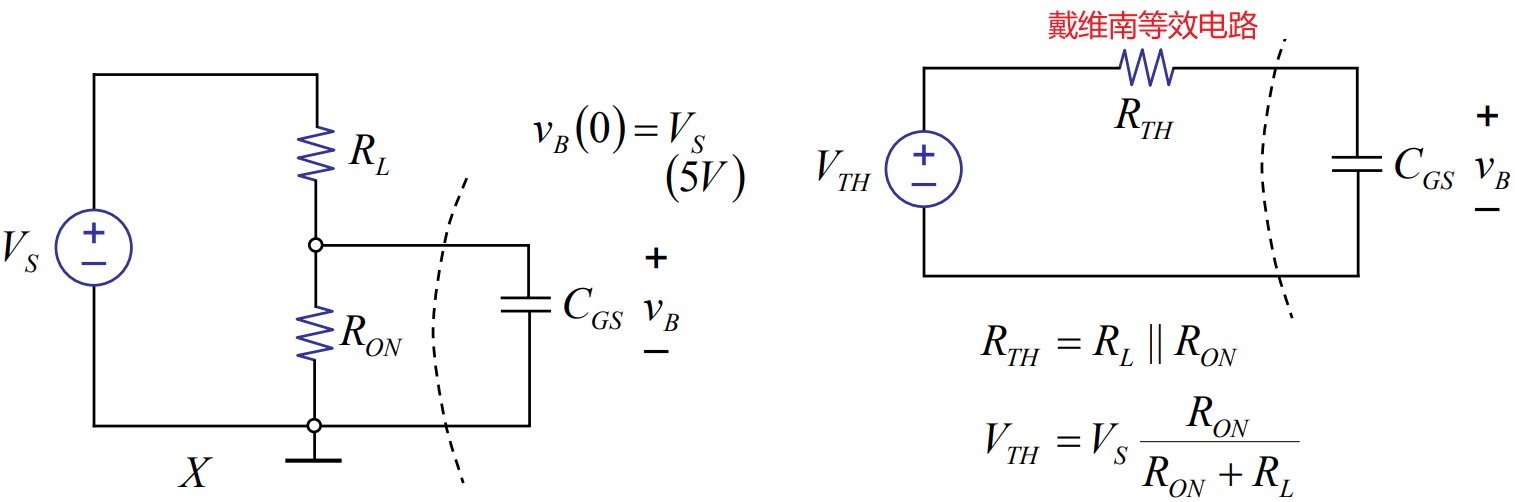

B点\(0 \rightarrow 1\)的equivalent circuit如下:

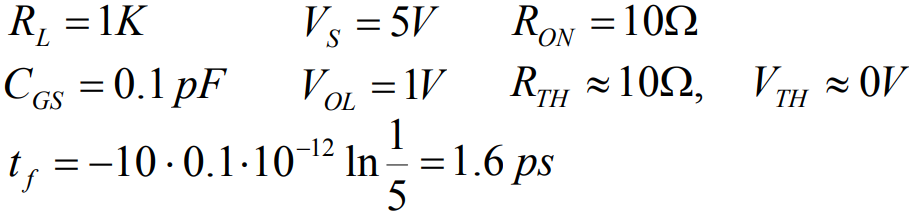

根据上一节的计算结果我们知道\(v_B=V_S+\left(0-V_S\right) e^{\frac{-t}{R_L C_{G S}}}\),令\(v_B=V_{O H}\),即可求得上升延迟时间$$ t_r=-R_L C_{G S} \ln \frac{V_S-V_{O H}}{V_S} $$实际的例子-1$$ \begin{gathered} R_L=1 \mathrm{~K} \quad V_S=5 \mathrm{~V} \quad C_{G S}=0.1 \mathrm{pF} \quad V_{O H}=4 \mathrm{~V} \\ t_r=-1 \times 10^3 \times 0.1 \times 10^{-12} \ln \frac{5-4}{5}=0.16 n s \end{gathered} $$B点\(1 \rightarrow 0\)的equivalent circuit如下:

根据\(v_B=V_{T H}+\left(V_S-V_{T H}\right) e^{\frac{-t}{R_{_{T H}} C_{_{G S}}}}\)以及\(v_B=V_{OL}\)求得下降延迟时间$$ t_f=-R_{T H} C_{G S} \ln \frac{V_{O L}-V_{T H}}{V_S-V_{T H}} $$实际的例子-2

时间常数(RC)是很重要的值,通常电路的延迟就在时间常数左右。比如实际的例子-1中RC = 0.1 ns,实际的例子-2中RC = 1 ps。

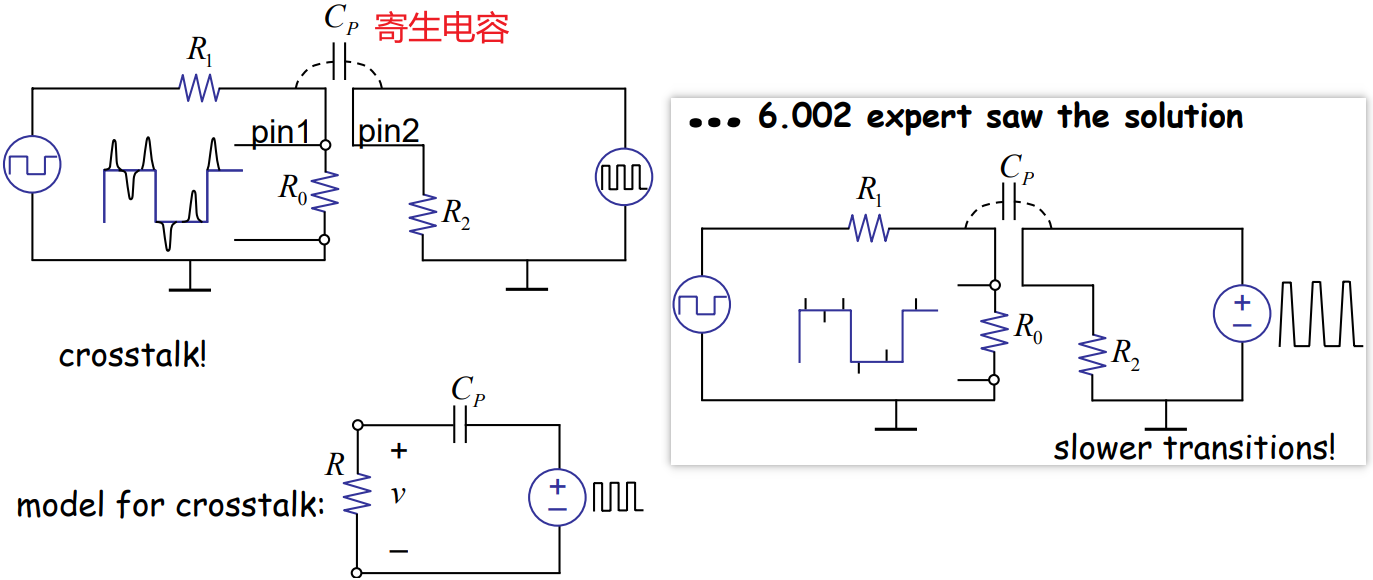

因为两个pin挨得太近了,在引脚之间有【寄生电容】(Parasitic capacitance),它的存在使得我们得到一个叫【串扰】(crosstalk)的东西,于是得到了一些尖峰。6.002的专家发现了解决方案,当transition变慢的时候也许会好些,所以我们用更慢的过渡来取代更快的。上图中的信号凸起和凹陷,可能使得电平进入了forbidden region。注意延迟并不一定取决于反相器本身,还取决于它所处的环境。

State and Memory

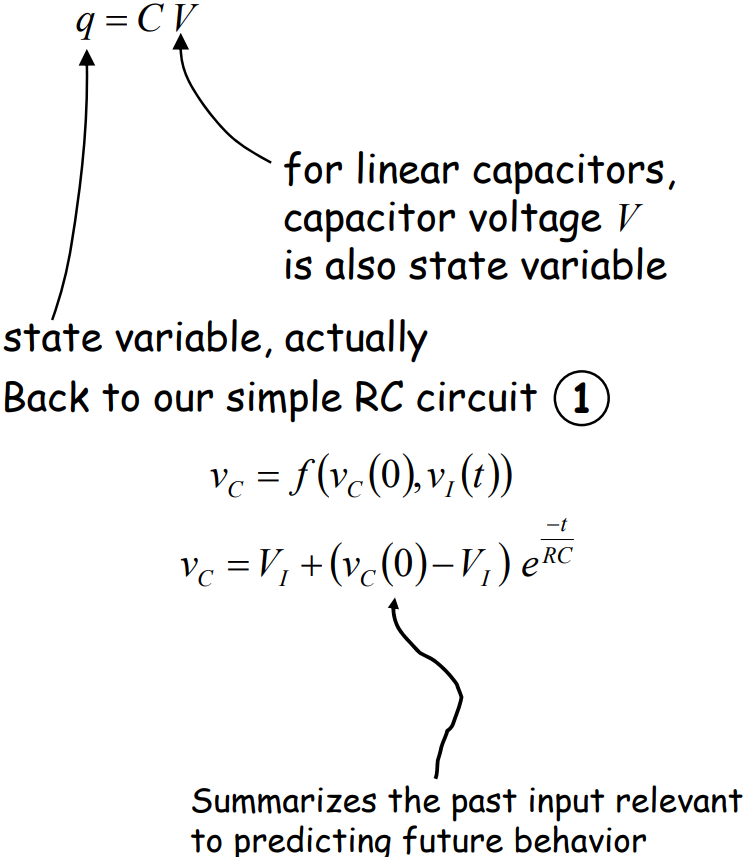

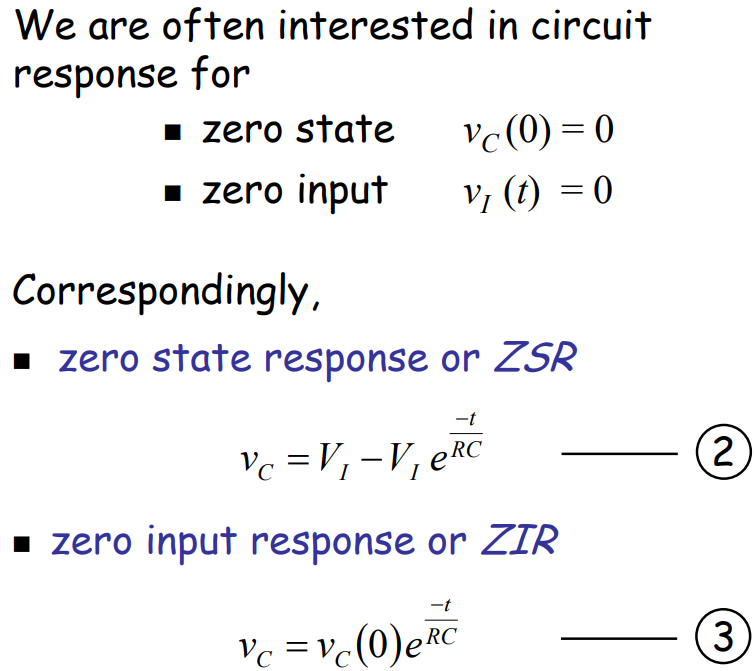

【DRAM】(Dynamic random access memory,动态随机存储器):你在每一台PC上都能找到DRAM,我们可以在里面的每个单元存储一个状态(实际上状态被存储在电容器中),并且在以后任何时间去会看它,只要我们不关掉机器的电源。 Notice that the capacitor voltage for \(t \geq 0\) is independent of the form of the input voltage before \(t=0\). Instead, it depends only on the capacitor voltage at \(t=0\), and the input voltage for \(t \geq 0\)

Notice that the capacitor voltage for \(t \geq 0\) is independent of the form of the input voltage before \(t=0\). Instead, it depends only on the capacitor voltage at \(t=0\), and the input voltage for \(t \geq 0\)

【State】 : summary of past inputs relevant to predicting the future

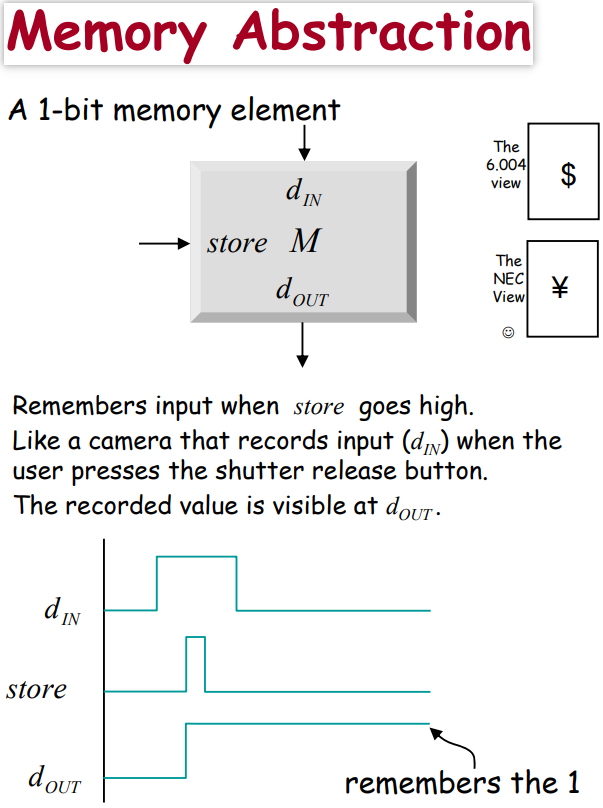

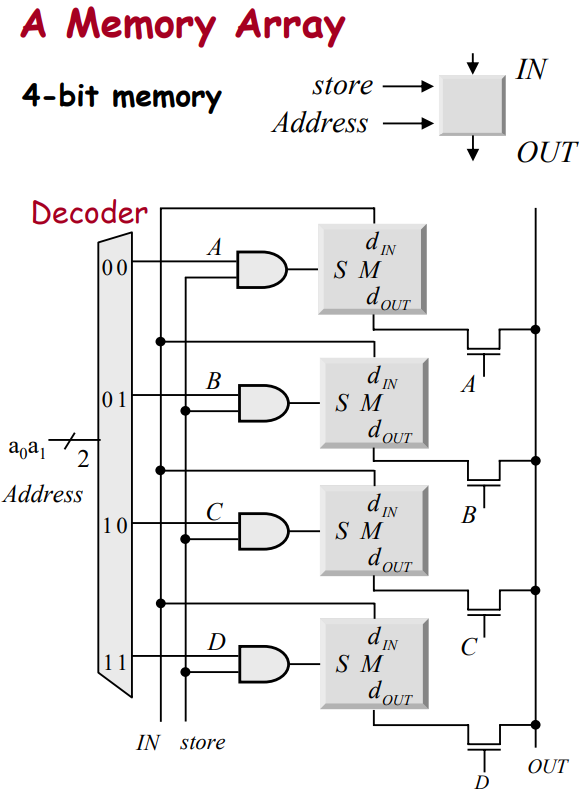

One application of STATE——DIGITAL MEMORY

Why memory? Or, why is combinational logic insufficient? 比如计算1+2+....,在labview中就是用移位寄存器,每次存放上一次加和的数据,相当于只需要一个加法器(adder)就能完成所有的计算。

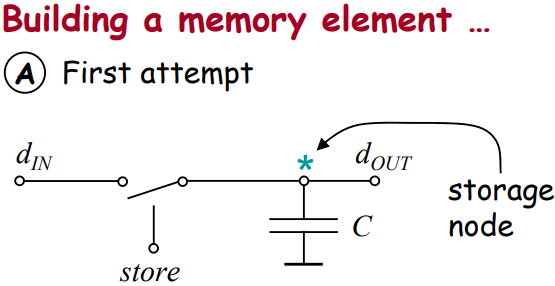

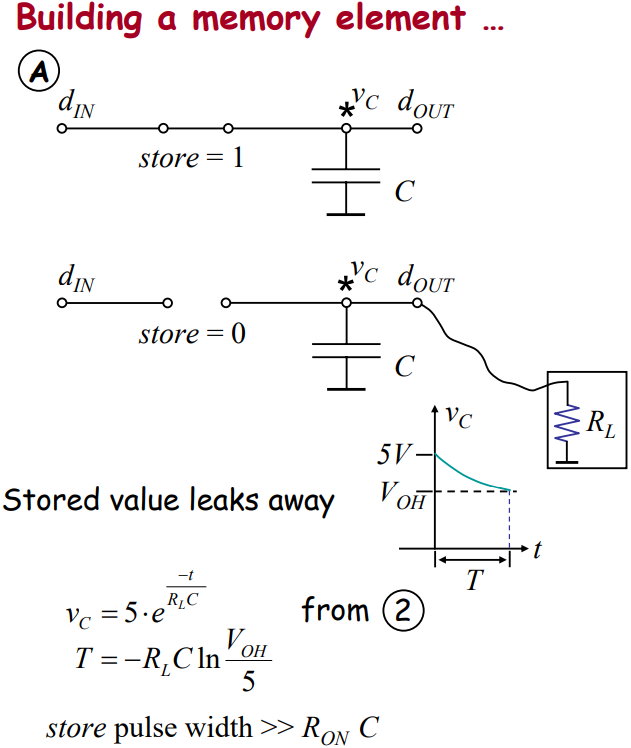

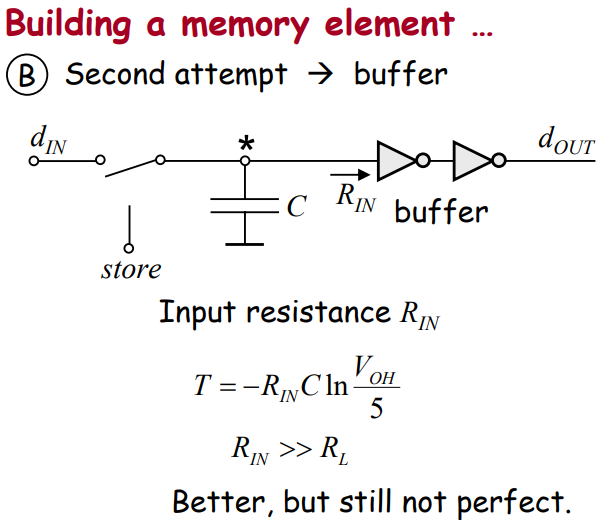

- Memory Abstraction图中,有一个隐含的假设(implicit assumption),也就是存储脉冲宽度要远远大于\(R_{ON}C\),其中\(R_{ON}\)是MOSFET的电阻,显然只有上述前提才能保证电容充满了,即准确反映出input的状态;

- MOSFET的导通电阻\(R_{ON}\)远小于\(R_L\);

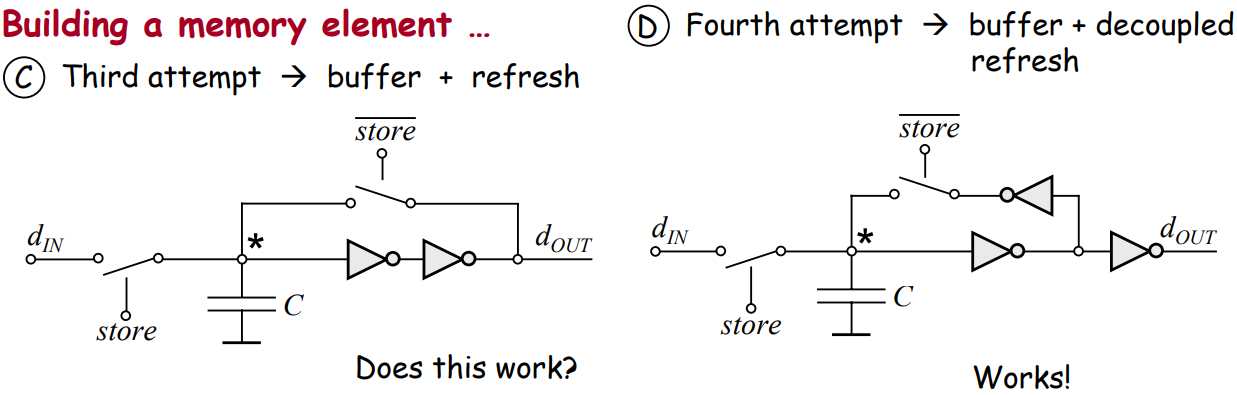

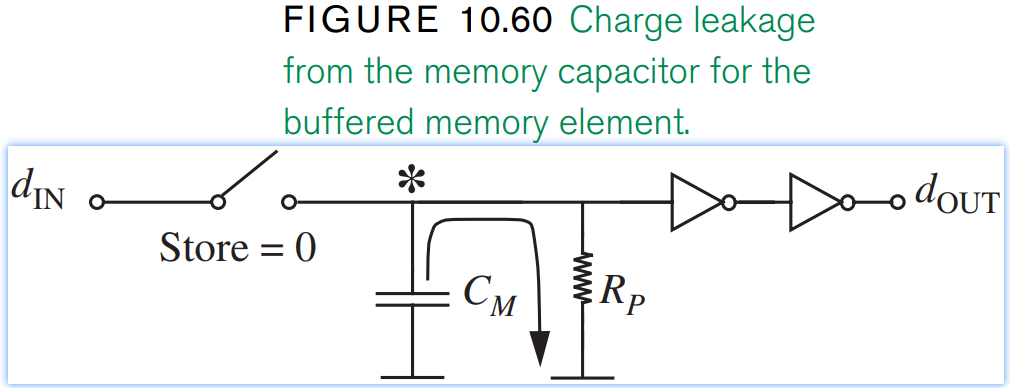

- 方案B的问题在于:In practice, capacitors will leak their charge over time due to parasitic resistances.

- 方案C,最上面那个开关(store上面一条横线)是store那个开关的状态取反,注意那个开关是和一个电源连接的,这样只要持续供电,电容里面的状态就可以保持,这就是【static memory】。图A和B都是【dynamic memory】。

The one-bit memory element that we have discussed thus far is called a dynamic one-bit memory element or a dynamic D-latch. It is dynamic in the sense that it stores a value written into it only for a finite amount of time (due to nonzero parasitic resistances in practical implementations). The static one-bit memory element or a static D-latch is another type of memory element that has the same logic properties as the dynamic D-latch, but can store a value written into it indefinitely. Figure 10.61 shows one possible circuit for a static memory element. In this circuit, a non-ideal switch with a very high ON resistance is connected between the power supply and the storage node of the memory element. When the output of the memory element is a logical 1, this switch is turned on and introduces a small stream of charge into the storage node to offset any leakage. Because it trickles charges into the node, this switch is called a trickle switch. The ON resistance of the trickle switch is made very large compared to the ON resistance of the store switch, so that the trickle input can be overridden easily by the input dIN.

- 方案D对比方案C,是为了提升dOUT引脚的抗干扰能力,这样external value cannot influence storage node from dOUT node.

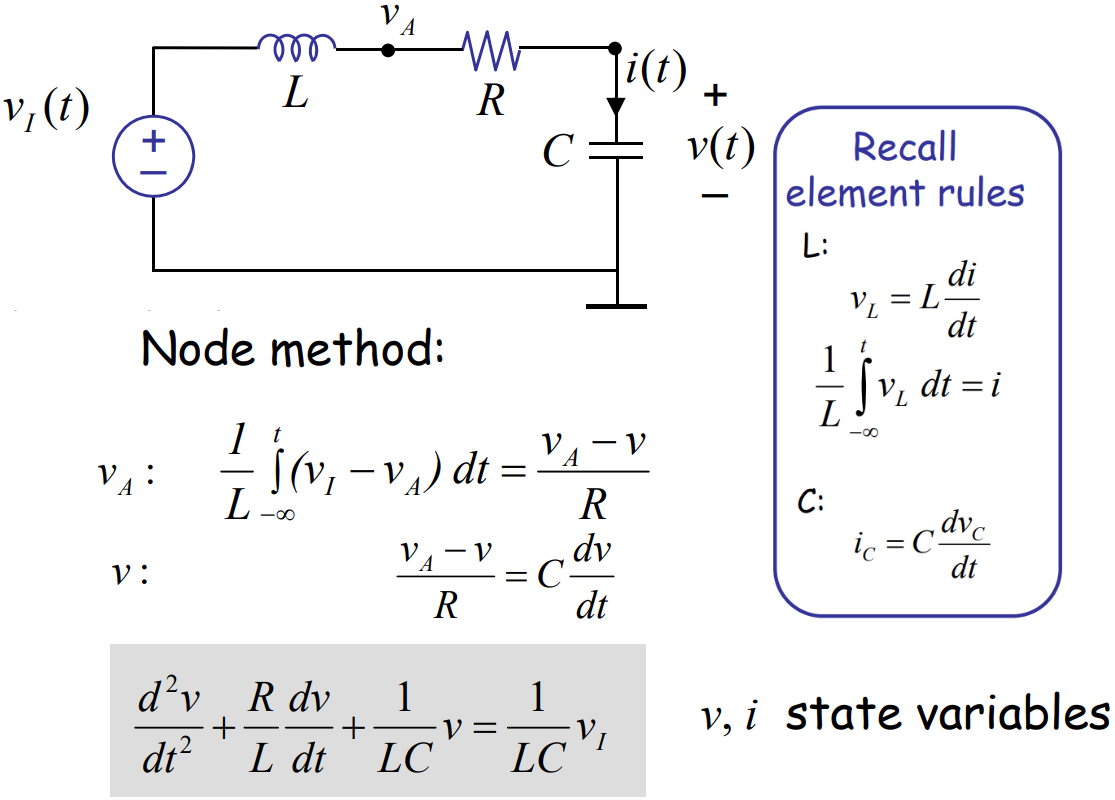

Second-Order Systems

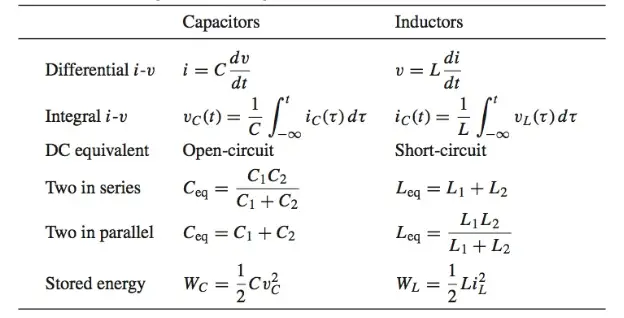

储能元件:

- 电容:存储的是是电荷,状态变化是电压,电压不能突变;the capacitor is one stubborn nut trying to hold its voltage

- 电感:把能量存储在磁场中,状态变化是电流,电流不能突变;the inductor is as stubborn. It is trying to hold its current.

每条导线,只要有电流通过,都会产生电感,因此实际的电路就是电阻+电感+电容。电路中有两个储能元件电容和电感,和单个存储元件时的动态特征有很大差别。不要因为讨论的例子中的寄生电容和寄生电感,就认为电容和电感是坏东西,因为寄生两个字似乎意味着是不好的东西,比如寄生虫。电容和电感本身是基本的集总元件,很多极为重要而且有用的电路设计中,我们需要电容和电感的存在。

EECS真正酷的地方在于,专家们用的方法其实是非常简单的,但前提是你需要建立一些直觉。

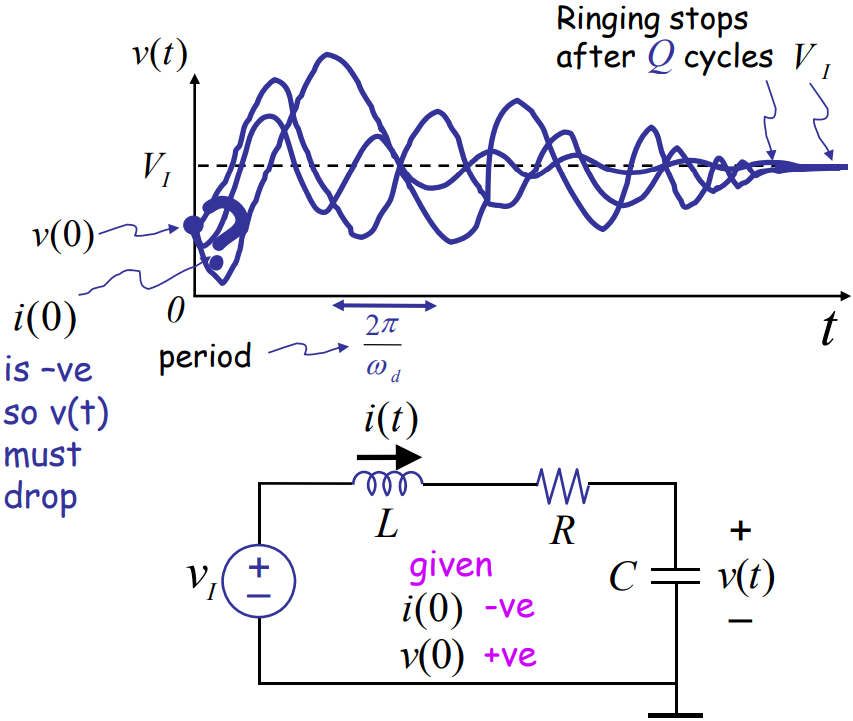

Our old friend, the inverter, driving another. The parasitic inductance of the wire and the gate-to-source capacitance of the MOSFET are shown.

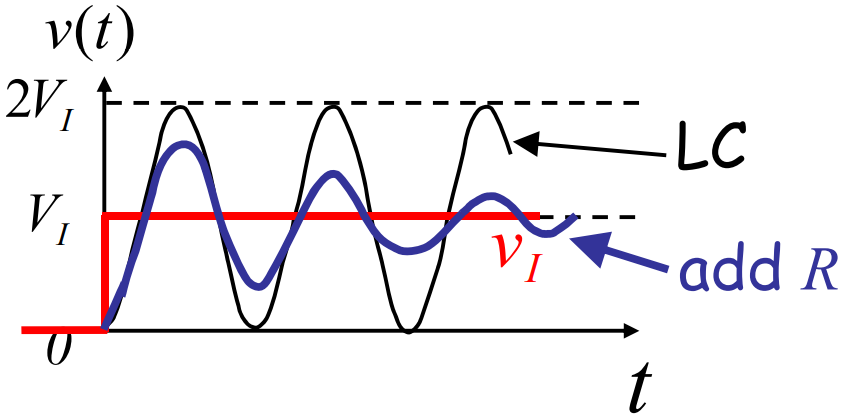

下面左图是RLC电路中电阻分别为2 KΩ时的节点A、B、C的电压(output)。Now, let’s try to speed up our inverter by closing the switch S to lower the effective resistance,即开关S闭合,RLC电阻的电阻变为50 Ω,output变为下面右图。

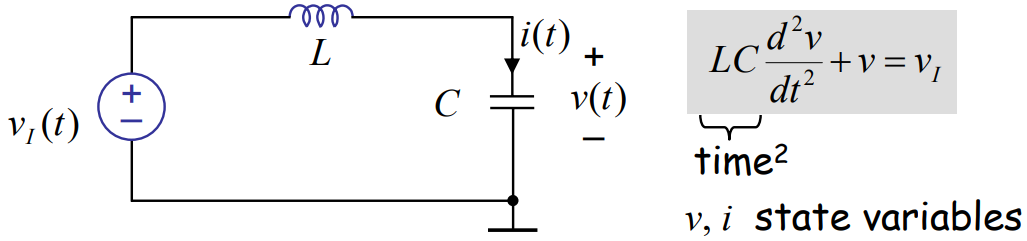

First, let’s analyze the LC network. 即先讨论更简单的LC电路。我们先复习一下电容和电感的特点:

于是很容易写出LC电路的方程:

对于齐次解,猜测解为\(v_H=A e^{s t}\),于是得到特征方程\(s^2=-\displaystyle\frac{1}{L C}\),得到\(s= \pm j \sqrt{\displaystyle\frac{1}{L C}}\)。令\(\omega_o=\sqrt{\displaystyle\frac{l}{L C}}\),于是\(v_H=A_l e^{j \omega_o t}+A_2 e^{-j \omega_o t}\)。

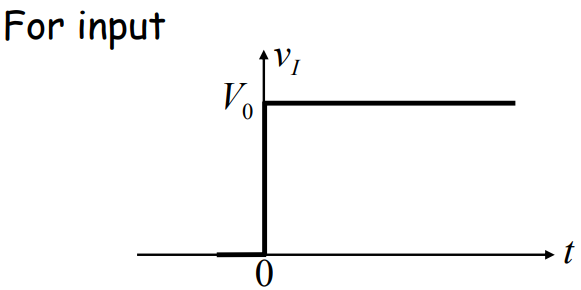

对于特解,在我们的设定中,\(v_I(t)\)是一个阶跃函数,即初始输入的阶跃信号,那么显然有\(v_P=V_0\)为特解。

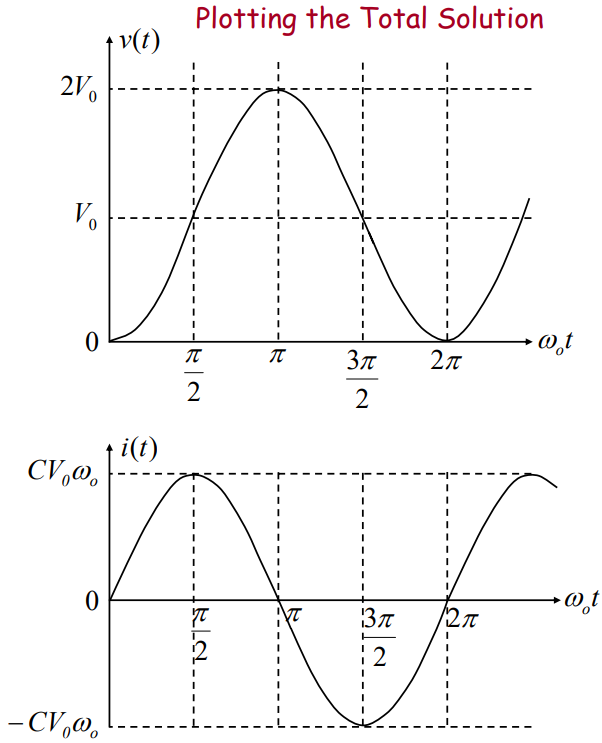

于是最后的通解为:$$ v(t)=V_0-\frac{V_0}{2}\left(e^{j \omega_o t}+e^{-j \omega_o t}\right) $$只考虑实部得到$$ \begin{aligned} &v(t)=V_0-V_0 \cos \omega_0 t\\ &i(t)=C V_0 \omega_o \sin \omega_o t \end{aligned} $$

Energy is sloshing back and forth between L and C. 课程视频第42分钟开始,老师讲解了这个动态过程,这和单摆(摆角小,无阻尼)的情况是一样的,能量在动能和势能之间转换。

- 最开始的时候输入为零,电路中没有电流,电容上也没有电荷,这两个储能元件也都没有存储任何能量;

- 然后电容不断被充电,直到电容两端的电压和电源电压\( V_0 \)一样大,即\(t=\pi/2\);

- 似乎电容两端的电压不应该继续增大,但是电感的特点是电流不能突变,于是电路还会继续维持原来的电流方向(惯性),即持续给电容充电,直到\(t=\pi\),而电容的特点是电压不能突变(hold the voltage),在这个过程中电容两端的电压继续增大到\( 2V_0 \);

- \(t=\pi\)时刻,虽然没有了电流,但是系统还是不能平衡,因为此时电容两端的电压比电源两端的电压还高\( V_0 \),于是反向驱动力的威力开始凸显,即电容开始放电(之前吞的能量,慢慢释放);

- 反向电流在\(t=3\pi/2\)时刻达到最大,此时电容两端的电压和电源电压再次平衡,似乎不用再吐出来,但是电感不答应,电感通过惯性继续维持之前的电流方向,让电容继续吐出能量,直到\(t=2\pi\),又回到原来的状态。

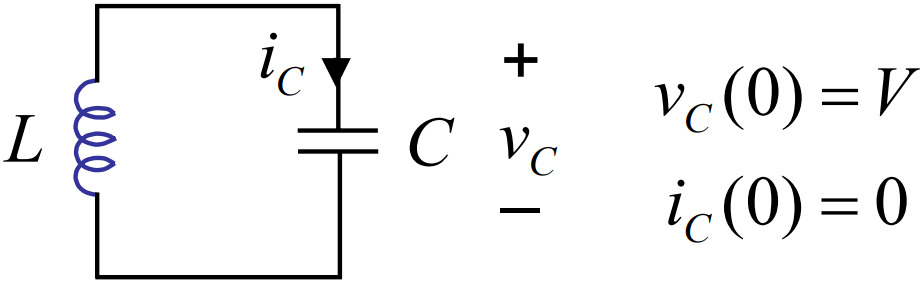

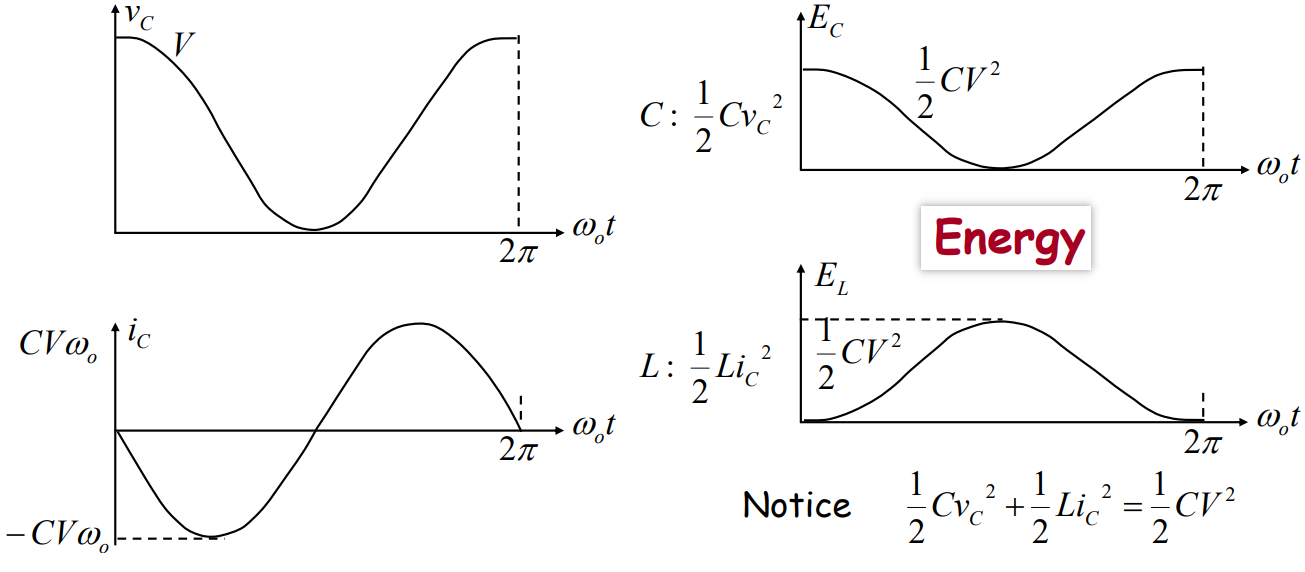

上面的情况是LC电路,然后给一个阶跃信号作为输入,然后求得最后的通解。下面我们举例学习另一个例子:没有外界输入,只给定初始条件,求解LC的各种物理量的响应特性。

We can obtain the answer directly from the homogeneous solution (\(V_0=0\)).$$ \begin{aligned} & v_C(0)=V \Rightarrow V=A_1+A_2 \\ & i_C(0)=0 \Rightarrow 0=C A_1 j \omega_o-C A_2 j \omega_o \end{aligned} $$最终解得$$ \begin{aligned} & v_C=V \cos \omega_o t \\ & i_C=-C V \omega_o \sin \omega_o t \end{aligned} $$

Total energy in the system is a constant, but it sloshes back and forth between the Capacitor and the inductor.

如果是RLC电路呢?最后给出下一节课的引子

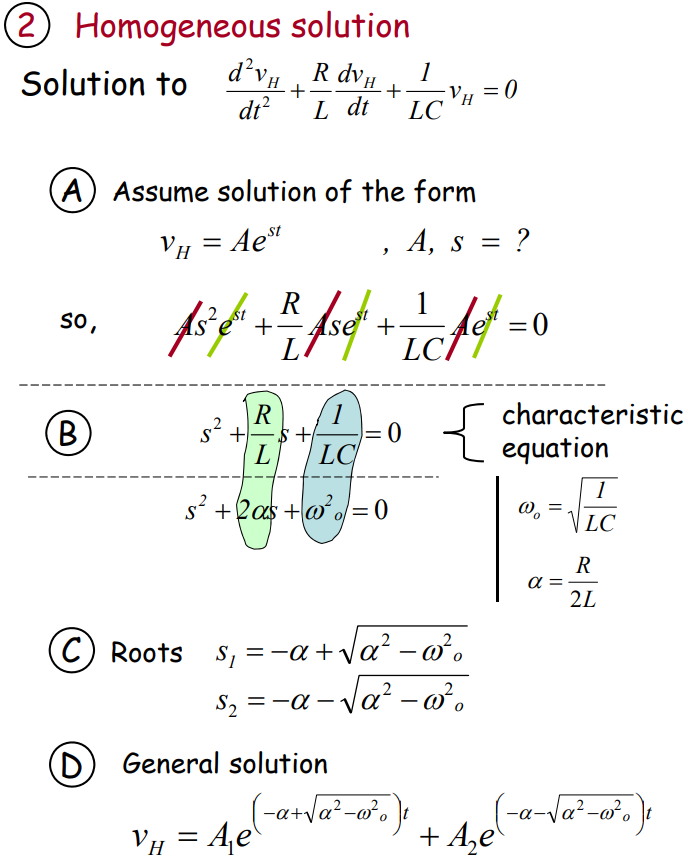

Damped Second-Order Systems

给定的input和初始条件如下:

特解:显然\(v_P=V_I\)满足条件。

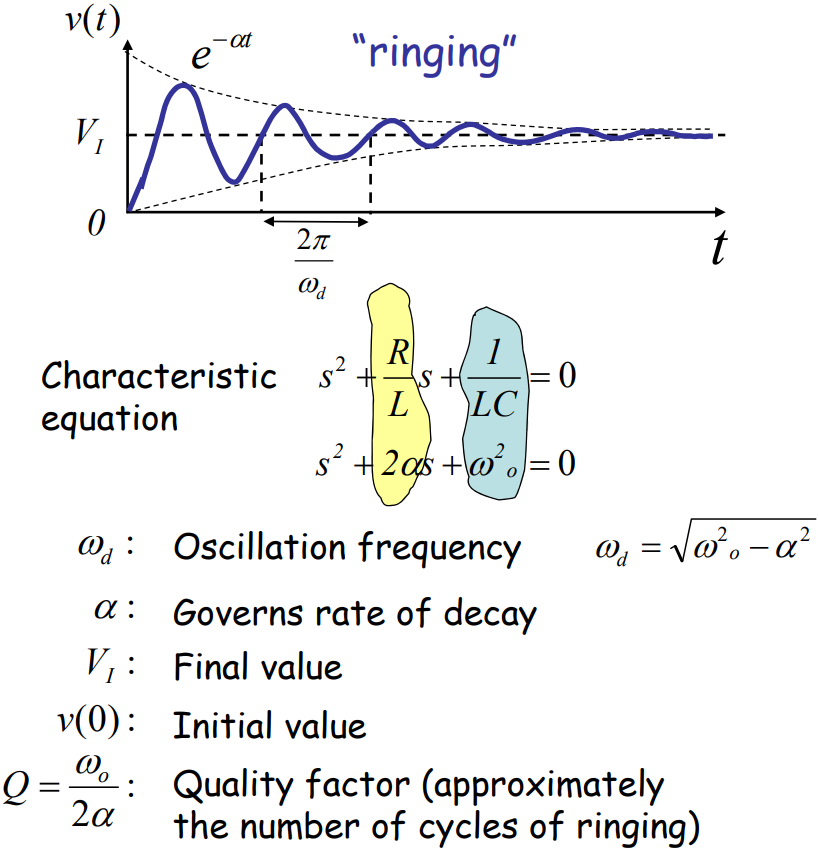

齐次解(Homogeneous solution):

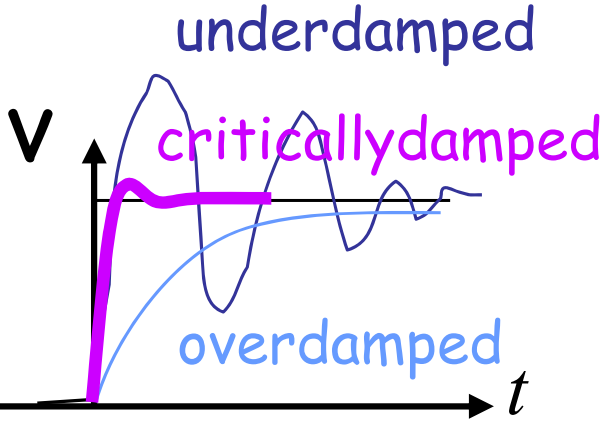

于是最终的Total solution为$$ \begin{gathered} v(t)=v_P(t)+v_H(t) \\ v(t)=V_I+A_1 e^{\left(-\alpha+\displaystyle\sqrt{\alpha^2-\omega_o^2}\right) t}+A_2 e^{\left(-\alpha-\displaystyle\sqrt{\alpha^2-\omega_o^2}\right) t} \end{gathered} $$Let’s stare at this a while longer…分三种情况讨论:

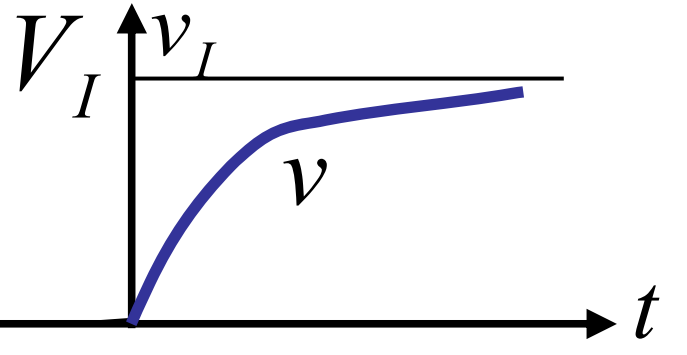

情形-1:Overdamped \(\alpha>\omega_o\)$$ v(t)=V_I+A_1 e^{-\alpha_1 t}+A_2 e^{-\alpha_2 t} $$其对应图形如下

情形-2:Underdamped \(\alpha<\omega_o\)根据初始条件,可以解得$$ v(t)=V_I-V_I e^{-\alpha t} \cos \omega_d t-V_I \frac{\alpha}{\omega_d} e^{-\alpha t} \sin \omega_d t $$注意:

- \(\omega_d=\sqrt{\omega_o^2-\alpha^2}\)

- For \(R=0 \Rightarrow \alpha=0\),于是\(v(t)=V_I-V_I \cos \omega_o t\),即Same as LC as expected。

对上面的结果进一步化简得到$$v(t)=V_I-V_I \frac{\omega_o}{\omega_d} e^{-\alpha t} \cos \left(\omega_d t-\tan ^{-1} \frac{\alpha}{\omega_d}\right)$$衰减项\(e^{-\alpha t}\)使得下图的蓝色的曲线的振幅越来越小。

情形-3:Critically damped \(\alpha=\omega_o\) 参见课本Section 13.2.3.

三种情形汇总得到下图

再谈情形-2 Underdamped (Intuitive Analysis,课本Sec. 12.7):$$ v(t)=V_I-V_I \frac{\omega_o}{\omega_d} e^{-\alpha t} \cos \left(\omega_d t-\tan ^{-1} \frac{\alpha}{\omega_d}\right) $$

- 最重要的四个参数:\(\omega_d\)、\(\omega_o\)、\(Q\)、\(\alpha \);

- 对于RLC电路的典型值,当R很小的时候,\(\alpha^2 \)也非常小,这就是欠阻尼的情形,也是现实中比较常见的情形,对于欠阻尼来说,\(\omega_d\)几乎等于\(\omega_o\);

- 品质引子\( Q\):

- 可以看作是振荡频率和阻尼之间的斗争,这个值指示了振荡了多少个周期,大约是Q个周期后振荡停止。

- large \( Q\) means "will oscillate for many cycles before stopping"

- small \( Q\) means "will oscillate for only a few cycles before stopping"

- I guess that people who work with oscillating systems tend to like the ones which keep going for many cycles.

- $$ \begin{aligned} & \text { decay in amplitude in one cycle }=e^{-(\pi / Q)}=\left(\frac{1}{e}\right)^{(\pi / Q)} \\ & \text { decay in energy in one cycle }=e^{-(2 \pi / Q)}=\left(\frac{1}{e}\right)^{(2 \pi / Q)} \end{aligned} $$

- after \(Q/\pi\) cycles, amplitude will be \(1/e\) of its original value

- after \( Q/(2 \pi)\) cycles, energy will be \(1/e\) of its original value

参考资料:

(1) Michael Richmond——The "Q" factor of an oscillating system

(2) 物理之旅——物理学中的类比

x